### LUCAS COMPASSI SEVERO

# UM FRAMEWORK PARA O DIMENSIONAMENTO AUTOMÁTICO DE BLOCOS A-NALÓGICOS BÁSICOS INTEGRADOS

Trabalho de conclusão de curso apresentado como parte das atividades para obtenção do título de Engenheiro Eletricista, do curso de Engenharia Elétrica do Campus Alegrete da Universidade Federal do Pampa, área de concentração Microeletrônica.

Orientador: Alessandro G. Girardi

### **ERRATA**

| Folha | Linha | Onde se lê | Leia-se |

|-------|-------|------------|---------|

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

|       |       |            |         |

Autoria: Lucas Compassi Severo

**Título:** Um Framework para o Dimensionamento Automático de Blocos Analógicos

Básicos Integrados

Trabalho de conclusão de curso apresentado como parte das atividades para obtenção do título de Engenheiro Eletricista, do curso de Engenharia Elétrica do Campus Alegrete da Universidade Federal do Pampa, área de concentração Microeletrônica.

# Os componentes da banca de avaliação, abaixo listados, consideram este trabalho aprovado.

|   | Nome                         | Titulação | Assinatura                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Instituição |

|---|------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1 | Alessandro Gonçalves Girardi | Doutor    | 1900                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | UNIPAMPA    |

| 2 | Sidinei Ghissoni             | Mestre    | Sudinei Glumi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UNIPAMPA    |

| 3 | Vinícius Jacques Garcia      | Doutor    | VINICIUS JACQUES JACQU | UNIPAMPA    |

Data da aprovação: 21 de Junho de 2011.

### **AGRADECIMENTOS**

Ao nos depararmos com os momentos de conclusões de trabalhos, é de grande importância lembrar que todos os desafios e oportunidades que temos no dia-a-dia, sejam profissionais ou pessoais, nós não as vencemos sozinhos, pois sempre há alguém para, de qualquer modo, ajudar-nos a atingir nossas metas e realizarmos nossos sonhos.

Desta forma, em homenagem a todos que de alguma forma colaboraram com o desenvolvimento deste trabalho de conclusão, bem como da graduação como um todo, eu manifesto o meu sincero agradecimento.

Agradeço ao professor Alessandro Girardi pela orientação durante os 4 anos de projetos de iniciação científica junto ao Grupo de Arquitetura de Computadores e Microeletrônica (GAMA) e aos desafios em mim impostos, os quais com certeza foram de grande importância para o desenvolvimento do trabalho e para o meu processo de aprendizagem. E à Fundação de Amparo à Pesquisa do Estado do Rio Grande do Sul (FAPERGS) pelo apoio financeiro ao projeto.

Agradeço aos colegas do curso de engenharia elétrica pela companhia durante a graduação bem como na amizade destes anos.

A meus pais e minha irmã Tamirís, que em toda a minha vida estiveram sempre me apoiando e dando-me forças para seguir na batalha de concretização de um sonho.

E a minha querida noiva Tanísia que está sempre ao meu lado nestas etapas de minha vida.

O único lugar aonde o sucesso vem antes do trabalho é no dicionário. Albert Einstein

### **RESUMO**

Este trabalho tem como objetivo o desenvolvimento de um framework para o projeto automático de circuitos integrados analógicos básicos em tecnologia CMOS. Para o projeto automático do circuito são utilizadas as heurísticas de otimização Algoritmo Genético (GA) e Simulated Annealing (SA), as quais exploram o espaço de projeto de forma eficiente para encontrar soluções otimizadas que atinjam algumas especificações requeridas. Nesta otimização cada uma das soluções geradas é avaliada com base na simulação elétrica SPICE. Como metodologias de projetos na ferramenta proposta foram inseridas a metodologia direta, na qual a heurística tem as dimensões do circuito como variáveis livres, e a metodologia gm/ID, que baseia-se em uma curva dependente somente da tecnologia de fabricação.

A ferramenta foi desenvolvida em ambiente Matlab® e possui uma interface gráfica amigável ao usuário. Desta forma, o framework proposto pode ser utilizado com uma ferramenta de pesquisa onde podem ser feitas comparações na automação do projeto de circuitos integrados analógicos básicos.

Como resultados, neste trabalho são mostrados projetos de um amplificador diferencial e de um amplificador OTA Miller, onde inúmeras comparações e análises são feitas.

Palavras-chave: Circuitos Integrados Analógicos, Ferramentas de Automação do Projeto, Framework, Inteligência Artificial.

#### **ABSTRACT**

The main goal of this work is the development of a framework for automatic design of basic analog integrated circuits in CMOS technology. For the design automations are used the optimizations heuristics Genetic Algorithms (GA) and Simulated Annealing which explore the design space for searching optimizated solutions that satisfy the design constraints. In this optimization the solution evaluations are performed with SPICE electrical simulations.

As design methodology, the proposal tool has the Direct Methodology where the heuristic works directly with the transistors sizes, and the  $gm/I_D$  Methodology which uses a curve that depend only by fabrication technology for the transistors sizing.

This tool was implemented in Matlab® and has a friendly graphical interface (GUI) with the human designer.

The proposed framework may be used as a tool for the researcher where several comparisons can be made in the Analog Integrated Design Automation.

As result we present the design automation of a Differential Amplifier and a Transconductance Amplifier Miller, where some comparisons and analysis are made.

Keywords: Analog Integrated Circuit, Electronic Design Automation Tool, Framework, Artificial Intelligence.

# LISTA DE ILUSTRAÇÕES

| FIGURA 1 – Dispositivo MOS de dois terminais (Capacitor MOS)                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURA 2 – Regiões de operação de um dispositivo de dois terminais: (A) acumulação, (B)                                                                |

| depleção e (C) inversão.                                                                                                                               |

| FIGURA 3 – Estrutura física de um transistor MOSFET                                                                                                    |

| FIGURA 4 – Curvas características: (A) $I_{DS}$ x $V_{DS}$ ( $V_{GS}$ =1, 2, 3, 4 e 5), (B) $I_{DS}$ x $V_{GS}$                                        |

| $(V_{DS}=5V)$ , $(C)$ $I_{DS}$ $x$ $V_{DS}$ $(V_{GS}=5$ $e$ $W/L=1$ , 2 $e$ 3), $(D)$ $I_{DS}$ $x$ $V_{GS}$ $(V_{DS}=5V$ $e$ $W/L=1$ , 2 $e$ 3), $(E)$ |

| gds x $V_{DS}$ ( $V_{GS}$ =5) e (F) gm x $V_{GS}$ ( $V_{DS}$ =5)                                                                                       |

| FIGURA 5 – Obtenção da Tensão de Early                                                                                                                 |

| FIGURA 6 – Fluxograma de projeto de circuito integrado analógico                                                                                       |

| FIGURA 7 – Típica curva gm/ID x IN para a tecnologia AMS 0.35μm                                                                                        |

| FIGURA 8 – Circuito Amplificador de Ganho intrínseco                                                                                                   |

| FIGURA 9 – Amplificado Diferencial com Carga Ativa                                                                                                     |

| FIGURA 10 – Esquemático do Amplificador OTA Miller                                                                                                     |

| FIGURA 11 – Circuito de simulação para a medição de Avo, GBW e PM                                                                                      |

| FIGURA 12 – Diagrama de Bode da análise AC do circuito da FIGURA 1139                                                                                  |

| FIGURA 13 – Configuração para medição de ICMR com análise DC                                                                                           |

| FIGURA 14 – Relação de entrada e saída para a medição do ICMR resultante da simulação do                                                               |

| circuito da FIGURA 13                                                                                                                                  |

| FIGURA 15 – Configuração para medição do Output Swing                                                                                                  |

| FIGURA 16 - Relação de entrada e saída para a medição do output swing resultante da                                                                    |

| simulação do circuito da FIGURA 15                                                                                                                     |

| FIGURA 17 – Circuito para medição de SR                                                  | <b>-1</b>  |

|------------------------------------------------------------------------------------------|------------|

| FIGURA 18 – Resposta de simulação do circuito da FIGURA 17 para medição do slew rate     |            |

| FIGURA 19 – Evolução da complexidade da tecnologia CMOS e das ferramentas de auxíli      | io         |

| ao projeto (HÄGGLUND, 2003)4                                                             | } <b>4</b> |

| FIGURA 20 – Evolução das ferramentas para o projeto de circuitos integrados analógicos d | le         |

| acordo com o grau de abstração (MARTENS, 2008)4                                          | 16         |

| FIGURA 21 – Pseudocódigo da técnica de otimização Simulated Annealing4                   | 18         |

| FIGURA 22 – Representação de um cromossomo dos algoritmos genéticos                      | ١9         |

| FIGURA 23 – Representação da recombinação e mutação em cromossomos binários: (A          | <b>\</b> ) |

| processo de recombinação, (B) processo de mutação5                                       | 50         |

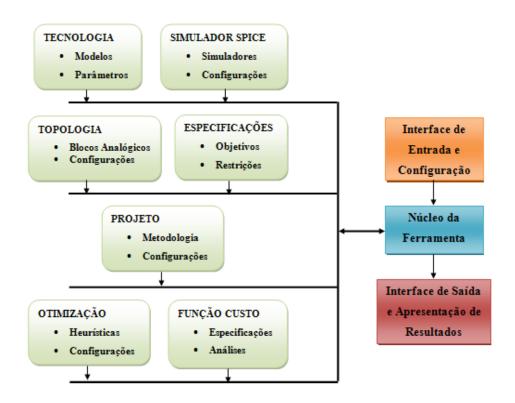

| FIGURA 24 – Diagrama de blocos da ferramenta proposta5                                   | 53         |

| FIGURA 25 – Diagrama de Blocos da Ferramenta                                             | 54         |

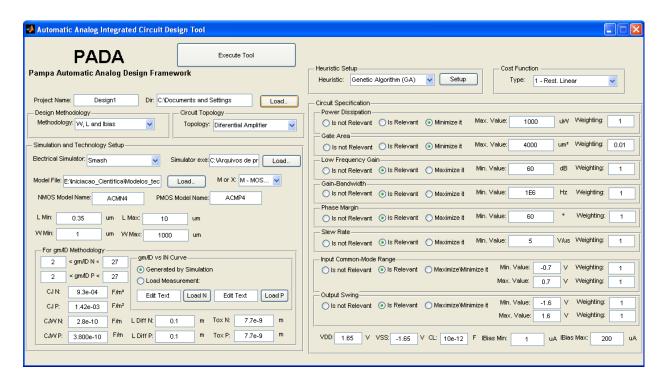

| FIGURA 26 – Interface gráfica de entrada de dados e configuração                         | 55         |

| FIGURA 27 – Códigos do núcleo da ferramenta: (A) execução da função, (B) código d        | le         |

| configuração e execução da heurística                                                    | 56         |

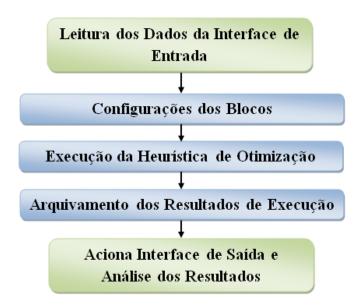

| FIGURA 28 – Funcionamento do bloco Núcleo da Ferramenta 5                                | 57         |

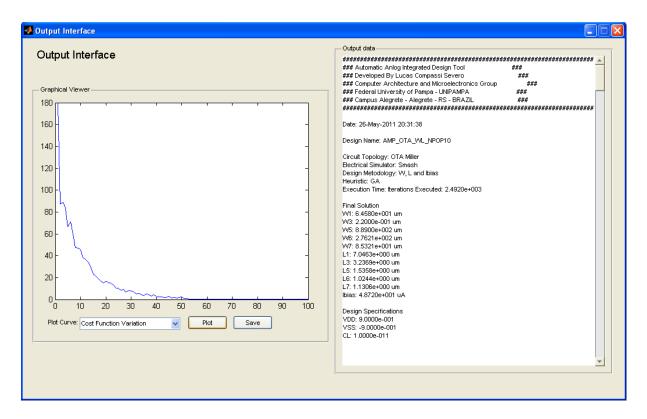

| FIGURA 29 – Interface gráfica de saída e apresentação dos resultados                     | 58         |

| FIGURA 30 - Arquivo de modelo de transistores MOSFET do tipo N e do tipo P, para         | a          |

| tecnologia AMS 0.35µm5                                                                   | 59         |

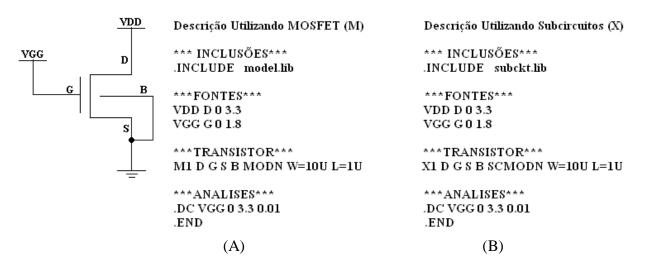

| FIGURA 31 – Descrição SPICE de transistores utilizando dispositivos : (A) MOSFETs (M)    |            |

| (B) subcircuitos (X).                                                                    | υÛ         |

| FIGURA 32 – Código para a medição de especificações do circuito por simulação elétric    |            |

| através da análise AC6                                                                   | 52         |

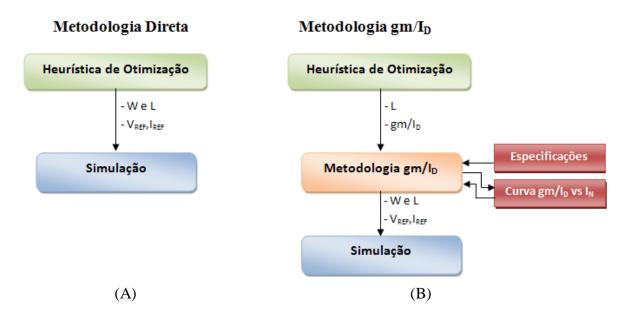

| FIGURA 33 – Metodologias de Dimensionamento do Framework: (A) metodologia direta, (B)                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------|

| metodologia gm/I <sub>D</sub>                                                                                                                     |

| FIGURA 34 – Código de configuração da heurística de otimização                                                                                    |

| FIGURA 35 – Curva gm/ID para a tecnologia AMS 0.35μm                                                                                              |

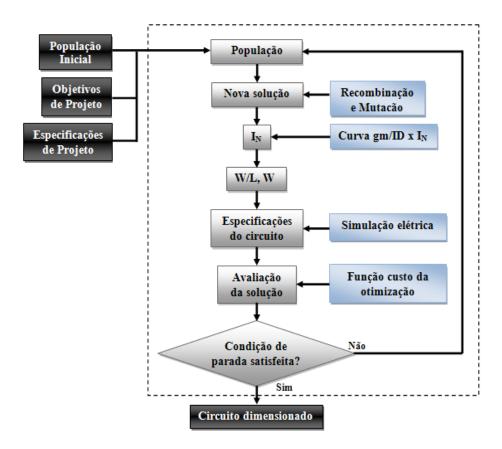

| FIGURA 36 – Fluxograma de otimização da ferramenta com algoritmo Genético e a metodologia gm/I <sub>D</sub> 69                                    |

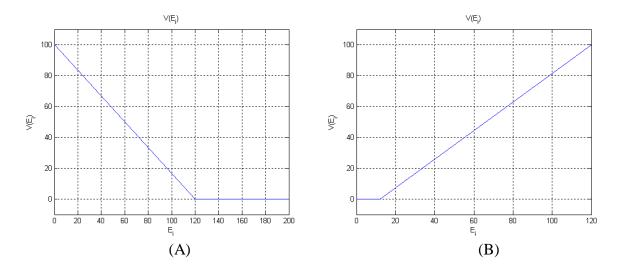

| FIGURA 37 – Variação do valor da restrição com relação ao valor da especificação: (A) restrição de valor mínimo, (B) restrição de valor máximo    |

| FIGURA 38 – Funções para o cálculo da função custo: (A) cálculo da função custo, (B) função de cálculo das restrições                             |

| FIGURA 39 – Curva gm/ID para a tecnologia AMS 0.35μm                                                                                              |

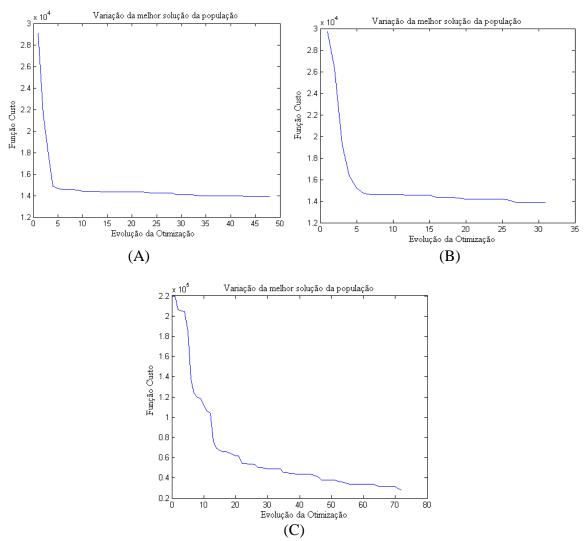

| FIGURA 40 – Evolução da função custo do melhor indivíduo da população: (A) projeto 1, (B) projeto 2 e (C) projeto 3                               |

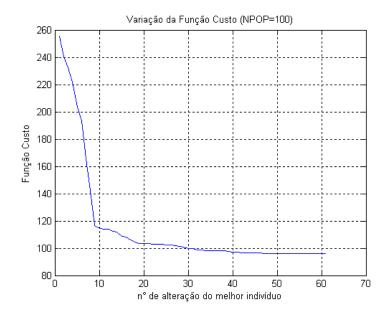

| FIGURA 41 – Evolução da Função Custo do melhor indivíduo da população para o projeto em tecnologia XH0.18µm com uma população de 100 indivíduos87 |

### LISTA DE TABELAS

| TABELA 1 – Especificações impostas ao projeto do Amplificador Diferencial                |

|------------------------------------------------------------------------------------------|

| TABELA 2 – Resultados do Projeto de um Amplificador Diferencial utilizando a Metodologia |

| Direta (W e L) com a Variação do Número de Indivíduos da população do Algoritmo          |

| Genético                                                                                 |

| TABELA 3 – Comparação entre Algoritmo Genético e Simulated Annealing no Projeto de um    |

| Amplificador Diferencial, utilizando a metodologia direta (W e L)                        |

| TABELA 4 – Conjunto de Especificações de Projeto de um Circuito Amplificador OTA Miller  |

| TABELA 5 – Resultados obtidos com no projeto do circuito Amplificador OTA Miller para    |

| três os conjuntos de especificações                                                      |

| TABELA 6 – Soluções Obtidas com a Execução da Ferramenta para os Três Projetos do        |

| Amplificador OTA Miller                                                                  |

| TABELA 7 – Resultados Obtidos no Projeto do Amplificador OTA Miller em tecnología        |

| XFAB XH0.18μm85                                                                          |

| TABELA 8 - Resultados Obtidos no Projeto do Amplificador OTA Miller em tecnología        |

| XFAB XH0.18µm, com a variação do número de indivíduos na população do GA                 |

| TABELA 9 – Resultados Obtidos no Projeto do Amplificador OTA Miller em tecnología        |

| XFAB XH0.18μm88                                                                          |

| TABELA 10 - Resultados Obtidos no Projeto do Amplificador OTA Miller em tecnología       |

| XFAB XH0.18µm com a heurística simulated annealing                                       |

| TABELA 11 - Resultados Obtidos no Projeto do Amplificador OTA Miller em tecnologia       |

| XFAR XH0 18um e AMS 0 35um                                                               |

| TABELA 12 - Resultados Obtidos no | Projeto do Amplificado   | or OTA Miller | em tecnologia |

|-----------------------------------|--------------------------|---------------|---------------|

| XFAB XH0.18μm e AMS 0.35μm com    | a heurística simulated a | ınealing      | 91            |

### LISTA DE ABREVIATURAS E SIGLAS

SPICE – Simulador com ênfase em circuitos integrados

GUI - Interface Gráfica de Usuário

MOSFET – Transistor de Efeito de Campo - Metal Óxido Semicondutor

NMOS – Transistor MOSFET do tipo N

PMOS - Transistor MOSFET do tipo P

SA – Técnica de Otimização Simulated Annealing

GA – Técnica de Otimização Algoritmo Genético

# **SUMÁRIO**

| Errata                                                                                            | 2  |

|---------------------------------------------------------------------------------------------------|----|

| Agradecimentos                                                                                    | 5  |

| RESUMO                                                                                            | 7  |

| Abstract                                                                                          | 8  |

| Lista de ilustrações                                                                              | 9  |

| Lista de tabelas                                                                                  | 12 |

| Lista de abreviaturas e siglas                                                                    |    |

| Sumário                                                                                           |    |

| 1 Introdução                                                                                      |    |

| 2 Projeto de circuitos integrados analógicos                                                      |    |

| 2.1 Circuitos Integrados                                                                          | 20 |

| 2.2 Tecnologia CMOS de transistores MOSFETs                                                       | 21 |

| 2.3 Projeto de Circuitos Integrados Analógicos em Tecnologia CMOS                                 | 27 |

| 2.3.1 Metodologia de projeto de circuitos integrados analógicos                                   | 29 |

| 2.4 Amplificadores Operacionais                                                                   | 33 |

| 2.4.1 Amplificador Diferencial                                                                    | 34 |

| 2.4.2 Amplificador OTA Miller                                                                     | 36 |

| 2.5 Medição de especificações de amplificadores através da simulação elétrica                     | 38 |

| 2.6 Conclusão                                                                                     | 42 |

| 3 Ferramentas de auxílio ao projeto de circuitos integrados Analógicos e Herísticas de otimização | 43 |

| 3.1 Introdução                                                                                    | 43 |

| 3.2 Ferramentas de Projeto Analógico                                                              | 44 |

| 3.3 Heurísticas de Otimização no Projeto de Circuitos Integrados Analógicos                       | 46 |

| 3.3.1 Simulated Annealing                                                                         | 47 |

| 3.3.2 Algoritmos Genéticos                                                                        | 48 |

| 3.3.3 Função Objetivo                                                                             | 50 |

| 3.4 Conclusão                                                                                     | 51 |

| 4 Framework para o projeto de circuitos integrados analógicos                                     | 52 |

| 4.1 Introdução                                                                                    | 52 |

| 4.2 Interface de Entrada de Dados e Configurações                                                 | 54 |

| 4.3 Núcleo da Ferramenta                                                                          | 55 |

| 4.4 Interface de Saída e Apresentação dos Resultados                                                          | 57  |

|---------------------------------------------------------------------------------------------------------------|-----|

| 4.5 Tecnologia                                                                                                | 58  |

| 4.6 Simulador SPICE                                                                                           | 61  |

| 4.7 Topologia                                                                                                 | 62  |

| 4.8 Especificações                                                                                            | 63  |

| 4.9 Projeto                                                                                                   | 64  |

| 4.10 Otimização                                                                                               | 67  |

| 4.11 Função Custo                                                                                             | 69  |

| 4.12 Conclusões                                                                                               |     |

| 5 Resultados                                                                                                  | 75  |

| 5.1 Introdução                                                                                                |     |

| 5.2 Amplificador Diferencial                                                                                  |     |

| 5.2.1 Automação do Projeto com GA com Populações de Tamanhos Distintos                                        |     |

| 5.2.2 Comparação GA e SA                                                                                      |     |

| 5.3 Amplificador OTA Miller                                                                                   |     |

| 5.3.1 Resultados Obtidos com a Tecnologia AMS 0.35µm                                                          |     |

| 5.3.2 Resultados obtidos com a tecnologia XFAB XH0.18µm                                                       | .84 |

| 5.3.3 Análise da variação do número de indivíduos na População                                                | .85 |

| 5.3.4 Comparação GA e SA em Tecnologia XH0.18µm                                                               | .87 |

| 5.3.5 Comparação entre tecnologias de fabricação de circuitos integrados                                      | .89 |

| 5.4 Conclusão                                                                                                 | 92  |

| 6 Conclusões                                                                                                  | 93  |

| 7 Resultados de Publicações                                                                                   | 94  |

| 7.1 Pesquisa Científica                                                                                       | 94  |

| 7.1.1 Prêmios acadêmicos                                                                                      | .94 |

| 7.1.2 Capítulo de livro                                                                                       | .94 |

| 7.1.3 Publicações em eventos nacionais e internacionais                                                       | .95 |

| Referências bibliográficas                                                                                    | 97  |

| Apêndice A - RELATÓRIO DE EXECUÇÃO GERADO PELA FERRAMENTA NO PROJETO DE UM CIRCUITO AMPLIFICADOR DIFERENCIAL1 | 00  |

| ANEXO 1 - ARTIGO SUBMETIDO PARA PUBLICAÇÃO NO "XI MICROELECTRONICS STUDENTS FORUM - SFORUM 2011"1             | 02  |

# 1 INTRODUÇÃO

Os responsáveis pelo desenvolvimento tecnológico da atualidade são os circuitos integrados. Não é difícil imaginar que os circuitos integrados estão presentes na grande maioria dos equipamentos que necessitam de circuitos eletrônicos. Com isso, os sistemas integrados estão presentes em todos os setores da economia. No setor primário os circuitos integrados são utilizados para a automatização das plantações agrícolas e no monitoramento de animais de pecuárias (CEITEC-SA, 2011). No setor secundário existe uma massiva utilização de circuitos para melhorar a quantidade e qualidade da produção, bem como substituir o homem em tarefas monótonas ou de risco. No setor terciário os circuitos integrados são ainda mais empregados. Entre as aplicações, se destacam as comunicações que possibilitam a troca de informações em tempo real e a área de saúde em que cada vez mais é possível de se fazer diagnósticos mais precisos e utilizar técnicas cada vez menos invasivas.

Com relação aos aspectos econômicos no mundo, a indústria de microeletrônica passou de US\$ 26 bilhões em 1986 para US\$ 256 bilhões em 2008, sendo que só no ano de 2010 o crescimento mundial do setor foi cerca de 30% (PETTEY, 2011). No Brasil, as exportações de componentes semicondutores passaram de US\$ 50 milhões em 2000 para US\$ 57 milhões em 2009 enquanto isso as importações passaram de US\$ 2 bilhões em 2000 para US\$ 3,2 bilhões em 2009, representando assim um enorme déficit na balança comercial (SWART, 2010).

Os circuitos integrados representam uma grande fatia dos recursos econômicos de um país e por isso exigem grandes desenvolvimentos e incentivos.

Os circuitos integrados são circuitos eletrônicos construídos em escalas micrométricas ou nanométricas sobre elementos semicondutores, em sua maioria silício. Estes circuitos são classificados principalmente de acordo com o tipo de sinal que trabalham. Desta forma, os circui-

tos integrados são classificados em: circuitos analógicos, digitais ou digitais e analógicos ao mesmo tempo (circuitos mistos).

Na atualidade, a maior parte dos circuitos são digitais, porém os circuitos analógicos sempre serão necessários, seja para a interface entre os sinais físicos, polarização de circuitos ou para a geração de sinais para circuitos digitais, entre outros.

Do ponto de vista de complexidade, os circuitos analógicos são mais complexos que os digitais quanto ao dimensionamento dos transistores que os compõe, pois nos circuitos digitais todos os transistores possuem tamanhos predefinidos, já para circuitos analógicos cada um dos transistores deve ser dimensionado separadamente. Quando analisado o número de transistores, os circuitos integrados digitais são mais complexos que os circuitos analógicos, pois os circuitos digitais podem possuir até alguns bilhões de transistores (STACKHOUSE, 2009) em quanto os circuitos analógicos não passam das centenas de transistores.

Segundo (GRAEB, 2007), em 2005 cerca de 75% dos circuitos integrados possuíam blocos analógicos em sua construção. Nestes chips, cerca de 20% da área são ocupadas por circuitos analógicos. Embora pouca, esta área representa 40% de todo o esforço de projeto. Além do grande esforço de projeto, as partes analógicas são responsáveis por cerca de 50% dos defeitos ocorridos no processo de desenvolvimento de um circuito integrado. Este percentual se deve basicamente ao fato de as ferramentas de automação do projeto de circuitos integrados analógicos serem pouco desenvolvidas quando comparada aos circuitos digitais. Com isso, torna-se cada vez mais necessário o desenvolvimento de ferramentas para o projeto de circuitos integrados que explorem de maneira eficiente o espaço de projeto em busca de soluções que atinjam requerimentos impostos em sua aplicação. Nestas ferramentas deve-se sempre manter o foco na miniaturização dos circuitos e na menor dissipação de potência.

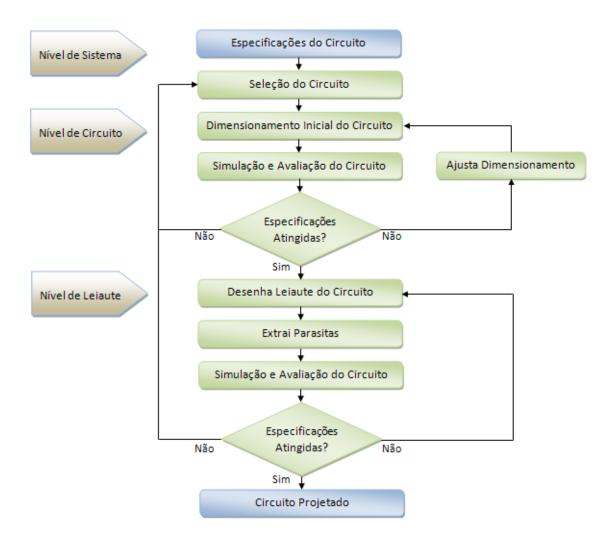

O projeto de um circuito integrado analógico é dividido em três grandes partes: nível de sistema, nível de circuito e nível de leiaute (BALKIR, 2003). Estes níveis se referem à abstração do projeto, onde no primeiro nível (sistema) o circuito é tratado como um bloco funcional. No segundo nível o circuito é representado pelo esquemático de transistores e o no nível de leiaute o circuito é tratado fisicamente através do desenho do dispositivo semicondutor.

No nível de circuito, o objetivo do projeto é sempre dimensionar cada um dos transistores que compõem um dado circuito de forma a satisfazer as restrições impostas ou especificações

mínimas de projeto. Como as metodologias de projetos não são bem definidas, a qualidade do projeto manual de um circuito integrado analógico depende da experiência do projetista.

Na automação do projeto de circuitos integrados analógicos existem inúmeros trabalhos de pesquisa com o objetivo de explorar o espaço de projeto com a utilização de técnicas de otimização não-linear e de inteligência artificial (GIELEN, 2000, VYTYAZ, 2009). Nestas ferramentas comumente são utilizados simuladores elétricos tipo SPICE¹ para prover informações acerca das soluções encontradas para um dado circuito baseando-se em modelos que representam o comportamento físico do dispositivo.

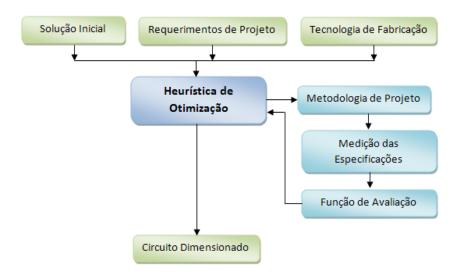

Neste panorama, este trabalho tem por objetivo o desenvolvimento de uma ferramenta para o projeto de blocos analógicos integrados básicos, com objetivo de explorar o espaço de projeto e dimensionar o tamanho dos transistores utilizando para isso técnicas de otimização de inteligência artificial. Com o objetivo específico deseja-se obter um framework para a análise e comparação de metodologias, técnicas de projeto e tecnologias de fabricação.

Para a implementação foi utilizado o ambiente de processamento matemático do Matlab® e a interface gráfica GUIDE (*Graphical User Interface Design Environment*) do mesmo software para possibilitar uma interface amigável ao usuário.

Este trabalho está organizado em 4 capítulos de forma que no Capítulo 2 será abordado o projeto de circuitos integrados analógicos em tecnologia CMOS (Metal Óxido Semicondutor Complementar), onde serão analisadas as técnicas e metodologias de projeto, bem como os blocos analógicos básicos que serão implementados na ferramenta. O capítulo 3 relata as ferramentas de CAD para circuitos integrados analógicos existentes e também apresenta as técnicas de otimização que serão utilizadas na ferramenta desenvolvida. O capítulo 4 trata do desenvolvimento do projeto, onde todas as partes do framework serão declaradas bem como o funcionamento de cada parte. O capítulo 5 trata da análise e comparação dos resultados encontrados com a ferramenta. Finalmente, o capítulo 6 apresenta as conclusões e recomendações de trabalhos futuros.

<sup>&</sup>lt;sup>1</sup> Simulador tipo SPICE são simuladores elétricos com ênfase em circuitos integrados

### 2 PROJETO DE CIRCUITOS INTEGRADOS ANALÓGICOS

### 2.1 Circuitos Integrados

Os circuitos integrados são sistemas eletrônicos construídos em escalas micrométricas e nanométricas sobre elementos semicondutores. Existem inúmeras tecnologias de fabricação de circuitos integrados, sendo que a mais utilizada atualmente é a tecnologia com transistores CMOS, que será detalhada no decorrer deste trabalho.

Os circuitos integrados, quanto ao seu tipo, dividem-se em três grandes grupos: circuitos digitais, circuitos analógicos e circuitos mistos. Os circuitos digitais são os que trabalham com sinais discretos em tempo e amplitude, como processadores, memórias, entre outros. Os circuitos analógicos trabalham com sinais contínuos em amplitude e tempo. São exemplos destes circuitos que fazem a interface entre os sinais físicos do mundo real e os circuitos de processamento digital, como amplificadores, filtros, conversores analógico-digitais e digital-analógicos, entre outros. O terceiro tipo de circuitos trata-se de circuitos que possuem tanto partes analógicas como digitais em um único chip. Entre as suas aplicações então os circuitos de rádio frequência, que possuem uma parte digital para a comunicação de dados e uma parte analógica para a modulação e amplificação do sinal de RF (LEE, 2003).

Este trabalho está focado no projeto de circuitos integrados analógicos, desta forma os demais tipos de circuitos não serão abordados no decorrer do trabalho.

### 2.2 Tecnologia CMOS de transistores MOSFETs

O termo CMOS tem seu nome derivado de Metal Óxido Semicondutor Complementar, pois se refere à composição construtiva do seu elemento principal que são os transistores MOSFETs (Transistor de Efeito de Campo Metal Óxido Semicondutor).

Quanto ao tipo do transistor o mesmo se deve ao tipo de dopagem do material semicondutor, ou seja, se for utilizados dopantes que resultam na sobra de elétrons na camada de valência do semicondutor eles são chamados de material do tipo N e os que resultam na falta de elétrons na camada de valência são chamados de elementos do tipo P, dando origem a transistores MOFETs do tipo N e do tipo P.

Os transistores MOSFETs foram inventados em 1960 pelos pesquisadores do Bell Labs nos Estados Unidos (RITCHIE, 1993) e a partir desta época foram os responsáveis pelo desenvolvimento tecnológico da era eletrônica e da informação. Atualmente, a utilização de transistores MOSFETs em circuitos integrados analógicos é dominante sobre o seu antecessor, o Transistor Bipolar de Junção (TBJ), que segundo (SCHNEIDER, 2010) possui características importantes para circuitos analógicos.

O nome MOS, se refere ao fato de o transistor fundamental ser formado por três camadas chamadas: Metal, Óxido e Semicondutor. Atualmente a camada de metal foi substituída por silício policristalino (polisilício), silício altamente dopado que apresenta características de um condutor.

Pela forma construtiva do dispositivo, havendo uma diferença de potencial entre o polisilício e o semicondutor, o dispositivo comporta-se como um capacitor de placas paralelas, de forma que se a tensão no polisilício for maior que a região do semicondutor, a camada acima do isolante apresentará cargas elétricas positivas e parte abaixo do isolante apresentará cargas negativas. O terminal de polisilício é comumente chamado gate, a região de carga negativa abaixo do isolante é chamada de canal e o semicondutor é chamado de substrato. Este dispositivo MOS possui dois terminais, gate e substrato.

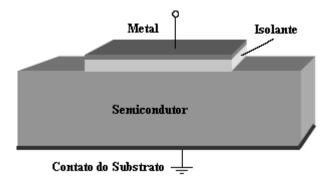

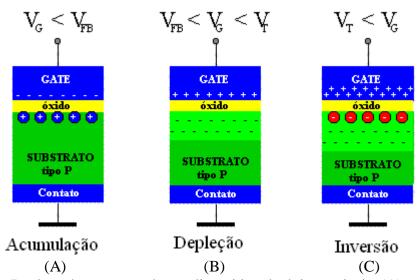

Assumindo um dispositivo MOS com substrato do tipo P, colocando contatos ôhmicos entre os dois terminais e tomando como referência o terminal do substrato, como mostrado na FIGURA 1, haverá no terminal de gate um potencial elétrico negativo devido ao material utilizado para a construção do gate, conforme ilustra a parte A da FIGURA 2. Este potencial de-

pende do material utilizado ou da função trabalho deste material (TSIVIDIS,2010). Nesta condição diz-se que o dispositivo esta operando na região de acumulação.

Ao aumentar o valor da tensão de gate chega-se a um ponto em que o potencial na superfície inferior do canal torna-se zero, ou seja, não existem mais cargas elétricas na região inferior ao isolante. Nesta condição o valor de tensão de gate é chamado de tensão de banda planar ou tensão de *flat band* ( $V_{FB}$ ) (TSIVIDIS,2010). Para valores de tensão de porta maiores que  $V_{FB}$  ocorre a formação de uma região de depleção abaixo do isolante, conforme mostra FIGURA 2-B.

Ao aumentar ainda mais a tensão de gate a região do canal começa a se formar. Quando a tensão de gate atinge um valor chamado de limiar (V<sub>T</sub>), o dispositivo passa a operar na região de inversão. O termo inversão se deve ao fato de uma região ocupada por portadores majoritários (no caso buracos) a partir de certo ponto torna-se ocupada por portadores minoritários (elétrons), ou seja, ocorre uma inversão de carga nesta região, conforme mostra a parte C da FIGURA 2. Quanto maior for a tensão de gate do transistor nesta região, diz-se que o transistor está mais fortemente invertido.

Devido a estes comportamentos, a capacitância equivalente de um dispositivo de dois terminais é basicamente a associação série de uma capacitância constante do óxido isolante (Cox), que depende da permissividade do óxido e da sua espessura, e uma capacitância do substrato devido ao aparecimento de uma região de depleção no substrato.

FIGURA 1 – Dispositivo MOS de dois terminais (Capacitor MOS)

FIGURA 2 – Regiões de operação de um dispositivo de dois terminais: (A) acumulação, (B) depleção e (C) inversão.

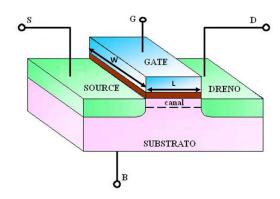

O dispositivo MOSFET além dos dois terminais (gate e substrato) apresenta mais dois terminais denominados de source e dreno os quais conectam as extremidades da região do canal através de regiões de difusão, conforme mostra a FIGURA 3. Utilizando a aproximação do canal gradual (SCHNEIDER, 2010), pode-se simplificar o funcionamento de um transistor MOSFET. Esta aproximação diz que a tensão de gate controla a carga presente no canal do dispositivo e a diferença de tensão entre os terminais de Dreno e Fonte controla o fluxo de corrente elétrica no canal. Segundo (SCHNEIDER, 2010), para modelar um transistor real, a partir da aproximação do canal gradual, devem ser acrescidos componentes que modelam transistores de canal curto e efeito da saturação de portadores na região do canal, entre outros.

Como pode ser visto na FIGURA 3, o MOSFET é um dispositivo simétrico, ou seja, a região de difusão de dreno é idêntica à região de fonte. Assim, o nome source ou dreno é uma mera questão de referência. Como referência adota-se para transistores do tipo N o source como sendo o terminal de menor potencial, e no tipo P é o de maior potencial.

Nesta figura, pode ser visto que o canal do transistor possui um valor de largura W e um valor de comprimento L. O tamanho do canal influencia diretamente na quantidade de carga elétrica presente no canal e por isso influencia em todas as características elétricas do dispositivo. Esta influência pode ser analisada com a Equação 1 que modela, de maneira simplificada, a corrente elétrica que flui entre os terminais de dreno e source e depende dos parâmetros da tecnologia (K'), da tensão de limiar (V<sub>T</sub>), das tensões terminais V<sub>GS</sub> e V<sub>DS</sub> e das dimensões do canal do transistor (W e L).

Nesta Equação, percebe-se que a corrente é proporcional a largura do canal (W) e inversamente proporcional ao comprimento do canal (L), ou seja, a corrente é diretamente proporcional a relação W/L. As dimensões W e L são as únicas variáveis livres no projeto de um transistor MOSFET.

$$I_{DS} = \begin{cases} K \frac{W}{L} \left[ V_{GS} - V_{T} - \frac{V_{DS}}{2} \right] V_{DS} &: V_{DS} < V_{GS} - V_{T} \\ K \frac{W}{2L} V_{GS} - V_{T}^{2} &: V_{DS} \ge V_{GS} - V_{T} \end{cases}$$

(1)

FIGURA 3 – Estrutura física de um transistor MOSFET.

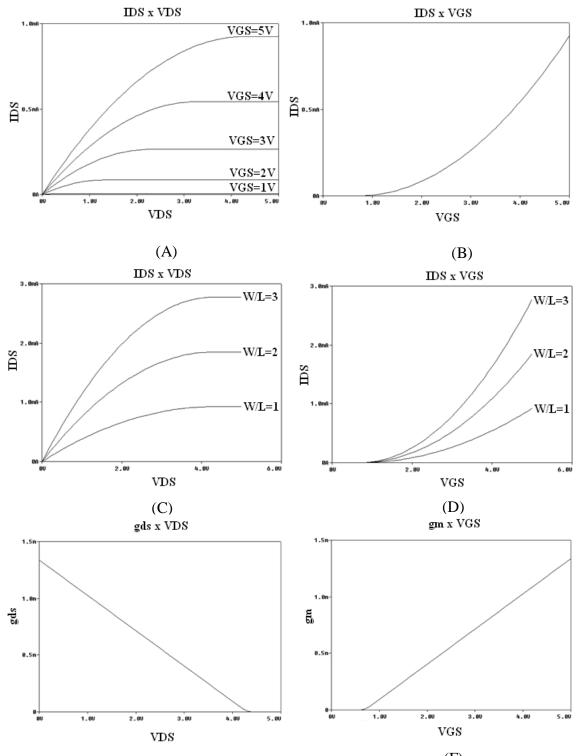

Para analisar o comportamento de um dispositivo MOSFET, podem-se utilizar duas curvas características. Estas curvas relacionam a corrente que flui entre os terminais de dreno e source ( $I_{DS}$ ) com as tensões terminais  $V_{GS}$  e  $V_{DS}$ . As curvas características de um transistor NMOS estão mostradas na

FIGURA 4. Na parte (A) desta figura, podem-se verificar as três regiões de operação de um transistor MOSFET, região de corte ( $I_{DS}$ =0A), região linear ou de triodo ( $I_{DS}$  varia linearmente com  $V_{DS}$ ) e região de saturação ( $I_{DS}$  aproximadamente constante). Na

FIGURA 4 – (B) é possível visualizar que  $I_{DS}$  é nulo para tensões  $V_{GS}$  menores que a tensão de limiar ( $V_T$ ), para  $V_{GS}$  maior que  $V_T$  a corrente  $I_{DS}$  aumenta quadraticamente com a tensão  $V_{GS}$ . Na

FIGURA 4 - (C) e (D) verifica-se que a corrente  $I_{DS}$  varia linearmente com a relação W/L, pois como mostrado na Equação 1 a corrente  $I_{DS}$  é proporcional a W/L.

Nas curvas características, verificam-se a variação da corrente  $I_{DS}$  com as tensões  $V_{GS}$  e  $V_{DS}$ , variações estas que são importantes quando são analisadas variações de pequenos sinais no dispositivo. As variações de  $I_{DS}$  devido a  $V_{GS}$  e  $V_{DS}$  são denominadas de transcondutância de gate (gm) e condutância de saída (gds) e são calculadas com as Equações (2) e (3), como as derivadas parciais da corrente  $I_{DS}$ . Na

FIGURA 4 – (E) e (F) estão mostradas curvas típicas de gm e gds.

$$gm = \frac{\partial I_{DS}}{\partial V_{GS}} \tag{2}$$

$$gds = \frac{\partial I_{DS}}{\partial V_{DS}} \tag{3}$$

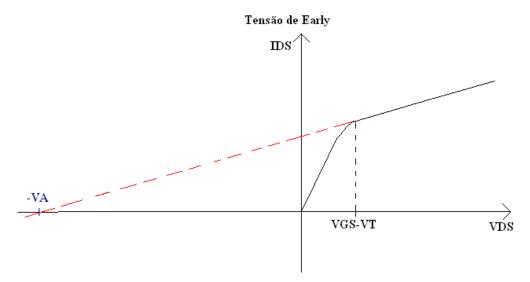

No comportamento analisado anteriormente, considerou-se que quando o transistor estiver operando em saturação ( $V_{DS} \ge V_{GS}$ - $V_{T}$ ) a corrente de dreno, na curva característica  $I_{DS}$  x  $V_{DS}$ , estabiliza-se em um valor de saturação dado pela Equação 1. Porém, na condição de saturação ocorre um efeito denominado de *pinch-off* que caracteriza-se pela redução no comprimento efetivo do canal. Assim, como o comprimento efetivo do canal é reduzido, a corrente tende a aumentar. Este aumento na corrente é relacionado com um parâmetro denominado de tensão de Early. A tensão de Early é obtida como a tensão  $V_{DS}$  em que a reta dada pela inclinação da corrente de dreno em saturação ultrapassa o eixo de corrente  $I_{DS}$  igual à zero, conforme ilustra a FIGURA 5. Outra forma para se obter a tensão de Early é utilizar a seguinte equação:

$$VA \simeq \frac{I_{DS}}{g\,ds} \tag{4}$$

Nesta Equação, toma-se o valor de VA na região em que o dispositivo opera em saturação.

Como a inclinação do aumento de corrente I<sub>DS</sub> em saturação é caracteriza-se pela redução no comprimento efetivo do canal do transistor, este efeito tende a ser reduzido com o aumento do comprimento do transistor, pois a variação no comprimento devido ao *pinch-off* torna-se percentualmente menos influente para transistores de canal longo.

FIGURA 4 – Curvas características: (A)  $I_{DS}$  x  $V_{DS}$  ( $V_{GS}$ =1, 2, 3, 4 e 5), (B)  $I_{DS}$  x  $V_{GS}$  ( $V_{DS}$ =5V), (C)  $I_{DS}$  x  $V_{DS}$  ( $V_{GS}$ =5 e W/L=1, 2 e 3), (D)  $I_{DS}$  x  $V_{GS}$  ( $V_{DS}$ =5V e W/L=1, 2 e 3), (E) gds x  $V_{DS}$  ( $V_{GS}$ =5) e (F) gm x  $V_{GS}$  ( $V_{DS}$ =5).

FIGURA 5 – Obtenção da Tensão de Early

Para a modelagem matemática de um transistor MOSFET é importante basear-se em equações que tenham parâmetros que possuam embasamento físico consistente. Desta forma, o objetivo de um bom modelo matemático é basicamente encontrar os fenômenos físicos que realmente influenciam no comportamento do dispositivo. Outra característica interessante é que o modelo preserve a simetria entre source e dreno do transistor e tenha como referência de tensão o terminal de substrato. Esta e outras características são encontradas no modelo ACM (MONTORO, 2007) o qual modela o dispositivo MOSFET baseando-se na carga do canal do dispositivo.

Também existem modelos que aproximam o comportamento real do dispositivo utilizando parâmetros físicos e uma série de parâmetros de ajuste de curva, de forma a aproximar o comportamento físico do dispositivo sem um embasamento físico consistente. Este tipo de modelo pode apresentar na ordem de cem parâmetros. Um exemplo deste tipo de modelo é o modelo BSIM 3 (MORSHED, 2011).

### 2.3 Projeto de Circuitos Integrados Analógicos em Tecnologia CMOS

O projeto de um circuito integrado analógico, segundo (BALKIR, 2003), pode ser dividido em três níveis de abstração: nível de sistema, nível de circuito e nível de layout. No Nível de sistemas um circuito analógico é tratado como um bloco funcional e por isso é o nível de maior abstração de projeto, pois é somente importante a função do bloco. Neste nível são definidas as especificações mínimas que o circuito deve ter para desempenhar a sua função. No

nível de circuito o nível de abstração é intermediário, pois neste nível o bloco é tratado como um esquemático de transistores, os quais devem ser dimensionados de acordo com as especificações dadas pelo nível de sistema. Finalmente, no nível mais baixo de abstração, nível de layout, é apresentado o desenho físico do circuito integrado. Para este nível são utilizados os tamanhos dos transistores calculados no nível anterior e levado em conta algumas restrições de desenho dadas pela fábrica de circuitos integrados (*Foundry*) que irá implementar o projeto em silício ou por restrições que afetam as especificações do circuito.

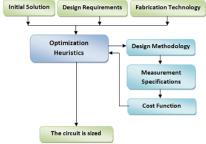

Na FIGURA 6, está mostrado um típico fluxo de projeto de circuitos integrados analógicos, onde os primeiros dois blocos pertencem ao nível de sistema. Neste nível são especificados os requerimentos de projeto desejado, e baseando-se nestes a topologia de circuito é escolhida. Já no nível de circuito a topologia escolhida é dimensionada utilizando-se uma metodologia de projeto manual, que será tratada na próxima seção, de forma a se obter uma solução inicial para o projeto. Baseando-se na simulação SPICE do circuito, as especificações são medidas e comparadas com os valores requeridos. Se os valores requeridos foram satisfeitos, passa-se então para o nível de leiaute. Caso as especificações não sejam atingidas deve-se retornar ao dimensionamento e ajustar os valores ou até mesmo retornar ao nível de sistema e escolher uma nova topologia de circuito que consiga atender às especificações requeridas.

Em nível de leiaute, tendo-se as dimensões dos transistores, deve-se desenhar os transistores obedecendo-se algumas regras de projeto e também técnicas de desenho com o objetivo de não prejudicar as especificações do circuito (HASTINGS, 2005). A partir do leiaute é extraído um circuito que contém todas as componentes parasitas, como capacitâncias e resistências, que ocorrem devido as resistência elétricas dos materiais e das sobreposições de camadas que compõem o leiaute de um circuito integrado. Após isso se deve, novamente, simular o circuito e comparar as especificações requeridas. Caso os resultados sejam satisfatórios o circuito está projetado, caso contrário, pode-se ajustar o desenho do leiaute, ajustar em nível de circuito o dimensionamento ou até mesmo em nível de sistema adotar outra topologia de circuito de forma a atingir todos os requerimentos desejados.

Este trabalho está focado no segundo nível de abstração, nível de circuito. Como dito anteriormente, a tarefa do projeto em nível de circuito é basicamente dimensionar cada um dos transistores que compõem o circuito integrado baseando-se nas especificações requeridas para

o projeto. Este dimensionamento se dá de forma a calcular as dimensões W (largura) e L (comprimento) do canal do transistor.

FIGURA 6 – Fluxograma de projeto de circuito integrado analógico

### 2.3.1 Metodologia de projeto de circuitos integrados analógicos

Em nível de circuito o fluxo de projeto necessita de uma metodologia para o dimensionamento dos transistores. Metodologia esta que relaciona os valores requeridos para as especificações com o tamanho dos transistores dos transistores que mais afetam as especificações.

Porém muitas vezes devido à dificuldade em dimensionar os transistores, bem como de haver inúmeras soluções possíveis, ou também pelo fato de um espaço de projeto altamente

restrito, encontrar uma solução para o circuito não é direta, necessitando assim inúmeros redimensionamentos. Neste contexto diz-se, que a qualidade de um projeto manual de circuitos analógicos muitas vezes está relacionada com a experiência do projetista, o que faz com que sejam necessários muitos anos de prática para o projeto de bons circuitos.

(ALLEN,2002) apresenta uma série de passos para o projeto manual de algumas topologias de circuitos analógicos. Seguindo esta metodologia e utilizando-se equações simplificadas que modelam o comportamento do circuito, chega-se a uma solução inicial para o circuito que muitas vezes não satisfaz as especificações requeridas. Assim, deve-se verificar os transistores que afetam mais a especificação não atingida para fazer neste um ajuste fino. Estes ajustes muitas vezes afetam outras especificações, o que torna o projeto uma sequência de ajustes.

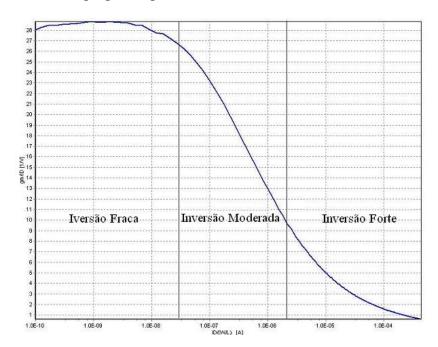

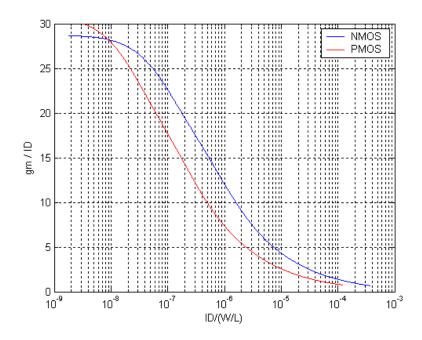

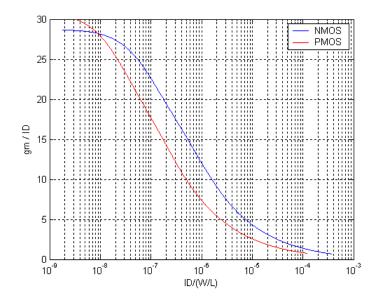

Outra metodologia de projeto manual é proposta por (SILVEIRA, 1996), chamada de metodologia gm/ID, na qual é utilizada uma curva como base para o dimensionamento dos transistores. Esta curva relaciona a transcondutância de gate pela corrente de dreno do transistor (gm/I<sub>D</sub>) versus a corrente normalizada (I<sub>N</sub>). A corrente normalizada (I<sub>N</sub>) é dada pela divisão da corrente de dreno (I<sub>D</sub>) pela relação W/L.

Como esta curva está relacionada a uma corrente normalizada, ela é única para uma dada tecnologia. Assim sendo, não depende das dimensões dos transistores e pode ser utilizada como base para o dimensionamento. Uma típica curva gm/ $I_D$  x  $I_N$  é mostrada na FIGURA 7.

O funcionamento desta metodologia se dá da seguinte forma: pelas especificações requeridas no projeto se obtem a transcondutância (gm) e a corrente de dreno ( $I_D$ ) necessárias para satisfazer a especificação. Tomando a relação gm/ $I_D$  com os valores obtidos, utiliza-se a curva da gm/ $I_D$  x  $I_N$  para obter o valor de  $I_N$  relacionado ao valor gm/ $I_D$ . Com o valor de  $I_N$  a relação W/L do circuito é obtida pela expressão (5). Tendo-se a relação W/L, pode-se ajustar o valor de L e obter o W até que as especificações sejam atingidas.

$$\frac{W}{L} = \frac{I_D}{I_N} \tag{5}$$

A metodologia gm/I<sub>D</sub> tem um embasamento físico interessante pelo fato de o valor gm/I<sub>D</sub> representar o grau de eficiência do transistor, de forma que quanto maior for este valor maior será a transformação de uma variação na tensão de gate em uma variação de corrente de dreno.

Outra característica interessante é fato do valor de gm/I<sub>D</sub> estar relacionado ao nível de inversão dos transistores, de maneira que valores pequenos de gm/I<sub>D</sub> indicam inversão forte e valores grandes indicam inversão fraca conforme pode ser visto na FIGURA 7. Neste mesmo contexto uma característica interessante é que com esta metodologia os transistores podem ser polarizados na região de inversão moderada, sendo que este tipo de polarização dificilmente é conseguido com as técnicas propostas por (ALLEN, 2002), conforme relata (CORTES, 2003).

FIGURA 7 – Típica curva gm/ID x IN para a tecnologia AMS 0.35μm.

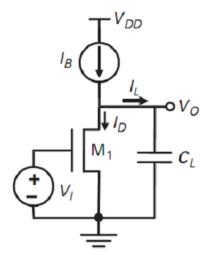

Para exemplificar as metodologias de dimensionamento manual, será utilizado um circuito amplificador de ganho intrínseco, cujo esquemático é mostrado na FIGURA 8. Este circuito trata-se de um amplificador de source comum e é formado por uma fonte de corrente  $I_B$ , um transistor M1 e um capacitor de carga  $C_L$ .

Este circuito possui duas especificações principais de funcionamento, especificações estas que servem de base para o dimensionamento do transistor M1 (W e L) e da corrente I<sub>B</sub>. As especificações são: ganho em baixa frequência (Avo) e produto ganho largura de faixa (GBW). O ganho em baixas frequências é calculado com a equação abaixo:

$$Av_0 = -\frac{gm.VA}{I_D} \tag{6}$$

onde gm é transcondutância de gate do transistor M1, VA a tensão de Early e  $I_D$  a corrente de dreno.

FIGURA 8 – Circuito Amplificador de Ganho intrínseco.

O produto ganho-largura de faixa pode ser calculado com a equação seguinte:

$$GBW = \frac{gm}{2\pi . C_{I}} \tag{7}$$

Assumindo que sejam requeridos Av<sub>0</sub> mínimo igual a -1000 e GBW igual a 1 MHz. Como parâmetros têm-se a tensão de Early depende do comprimento do canal e varia em 130V/μm, K' igual a 216,7x10<sup>-6</sup> A/V<sup>2</sup> e C<sub>L</sub> igual a 10pF. Assumindo um comprimento de canal (L) igual a 1μm, a tensão de Early (VA) resultante é de 130V. Estes valores de parâmetros são valores típicos da tecnologia AMS 0.35μm.

Com a Equação 7 se obtém o valor de trancondutância (gm) igual a 62,83  $\mu$ S. Substituindo as especificações em (6), obtem-se a corrente  $I_D$  do transitor M1 igual a 8,16  $\mu$ A.

Com os dados iniciais de projeto calculados, parte-se para o dimensionamento dos transistores com as metodologias relatadas anteriormente.

Com a metodologia gm/ $I_D$ , tomam-se gm e  $I_D$  e calcula-se o valor de gm/ $I_D$ . Neste caso é obtido um gm/ $I_D$  igual a 7.69. Com este valor e a curva da FIGURA 7, o valor de  $I_N$  obtido é igual a 2.88 $\mu$ A. Com a Equação 5 e o valor de L igual a 1 $\mu$ m, é obtido o valor de W igual a 2.83  $\mu$ m. Assim com a metodologia gm/ $I_D$  o circuito está dimensionado, pois W e L foram calculados e a corrente  $I_B$  é igual à corrente  $I_D$  de 8.16  $\mu$ A.

Com a metodologia proposta por (ALLEN,2002), pode-se utilizar a equação simplificada da transcondutância de gate (gm) em saturação, para obter-se a relação W/L. Esta equação é dada como:

$$gm \simeq \sqrt{2K' \frac{W}{L} I_D} \longrightarrow \frac{W}{L} \simeq \frac{gm^2}{2K' I_D}$$

(8)

Onde K' depende dos parâmetros da tecnologia AMS 0.35 $\mu$ m. Com esta equação a relação W/L encontrada é de 1,12. Como L foi assumido em 1 $\mu$ m, W resulta em 1,12  $\mu$ m e  $I_B$  é igual à corrente  $I_D$  de 8.16  $\mu$ A.

Analisando os resultados obtidos com as duas metodologias, observa-se que as dimensões W e L do dispositivo estão próximas (1.12 µm e 2.83 µm). Para validar a solução encontrada deve-se simular o circuito e verificar se as especificações foram atendidas.

### 2.4 Amplificadores Operacionais

Os amplificadores operacionais (AmpOps) são blocos analógicos de enorme importância em circuitos analógicos. O principal objetivo destes circuitos é que seu funcionamento possa ser facilmente ajustado através de componentes externos ao bloco. Com isso estes dispositivos possuem inúmeras aplicações, entre as quais destacam-se: amplificadores, circuitos de condicionamento de sinal, filtros ativos, geradores de funções e circuitos de chaveamento (CA-THEY, 2003).

As características desejáveis de um amplificador operacional é que o mesmo apresente um ganho de tensão elevado (idealmente infinito), possua tensões de entradas (inversora e não-inversora) com níveis de tensões próximos de forma que exista uma terra virtual entre os terminais (BOYLESTAD, 1996) e tenha uma alta impedância de entrada e uma baixa impedância de saída.

Neste trabalho serão utilizados somente duas topologias de circuitos amplificadores operacionais, um amplificador diferencial e um amplificador operacional de transcondutância (O-TA) tipo Miller os quais serão detalhados na próxima subseção. A metodologia proposta no trabalho que será descrita no Capítulo 4 não se restringe somente aos circuitos que serão analisados, pois teoricamente pode ser aplicada a qualquer topologia de circuito.

### 2.4.1 Amplificador Diferencial

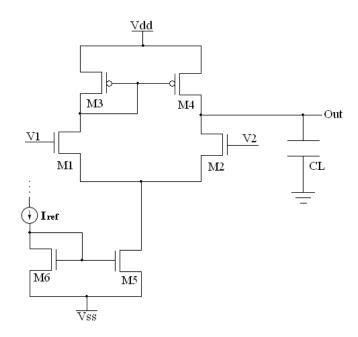

O amplificador diferencial é um dos blocos analógicos básicos mais versáteis. Este circuito é compatível com a tecnologia CMOS de circuitos integrados e serve como estágio de entrada para os amplificadores operacionais (ALLEN, 2002). Sua função básica é amplificar a diferença de tensão entre suas entradas. A FIGURA 9 mostra o esquemático de um amplificador diferencial com carga ativa.

O circuito é formado por um espelho de corrente de carga (formado pelos transistores M3 e M4), um par diferencial (formado pelos transistores M1 e M2), um espelho de corrente de referência (formado pelos transistores M5 e M6) e uma fonte de corrente de referência (I-ref).

FIGURA 9 – Amplificado Diferencial com Carga Ativa.

Neste circuito, devido à sua construção, são assumidas algumas igualdades quanto ao tamanho dos transistores, de forma que os espelhos de correntes possuam ganho de corrente unitário. Com isso M3 é igual a M4 e M5 é igual a M6. Além disso, o par diferencial de entrada deve ser exatamente igual para que o circuito amplifique a diferença de tensão entre as entradas. Com isso M1 e M2 possuem mesmas dimensões. Desta forma as variáveis livres do projeto deste circuito são W e L dos transistores M1, M3, M5 e a fonte de corrente de referência (Iref). Ou seja, o circuito tem 7 variáveis a serem dimensionadas.

No projeto do amplificador diferencial utilizando a metodologia gm/I<sub>D</sub>, as variáveis livres de projeto são o L e o valor de gm/I<sub>D</sub> de M1, M3 e M5, totalizando 6 variáveis de projeto, onde a partir da curva gm/I<sub>D</sub> x I<sub>N</sub> e das especificações do circuito são obtidos o W dos transistores e o valor da fonte de corrente Iref.

As principais especificações do circuito são: ganho de tensão em baixa freqüência  $(Av_0)$ , produto ganho-largura de faixa (GBW), slew-rate (SR), faixa de tensão no modo comum de entrada (ICMR), potência dissipada (Pdiss) e área (A).

O ganho em baixa frequência é a relação entre a tensão de entrada e de saída, definido como:

$$Av_0 = \frac{g_{m1}}{I_{D1}} (VA_2 + VA_4)$$

(9)

onde,  $g_{m1}$  é a transcondutância de gate do transistor M1 e  $VA_2$  e  $VA_4$  são as tensões de Early dos transistores M2 e M4, respectivamente.

O Slew Rate (SR) é a velocidade de resposta do amplificador em relação à variação de tensão em suas entradas, dado por:

$$SR = \frac{I_{ref}}{C_1} \tag{10}$$

onde, Iref é a corrente de referência e C1 é a capacitância total de saída. Esta capacitância é estimada com a soma da capacitância de carga CL e as capacitâncias de dreno de M2 e M4.

A faixa de tensão no modo comum de entrada (ICMR) define a máxima e a mínima tensão de entrada no modo comum, definidas por:

$$ICMR^{-} = V_{DS5(sat)} + V_{GS1} + V_{SS}$$

(11)

$$ICMR^{+} = V_{DD} + V_{GS3} + V_{TN1}$$

(12)

onde  $V_{DS5(SAT)}$  é a tensão de saturação do transistor M5,  $V_{GS1}$  e  $V_{GS3}$  são as tensões entre gate e fonte de M1 e M3, respectivamente,  $V_{DD}$  e  $V_{SS}$  são as fontes de alimentação do circuito e  $V_{TN1}$  é a tensão de limiar de M1.

Já o produto ganho-largura de faixa é dado por:

$$GBW = \frac{g_{m1}}{C_1} \tag{13}$$

Baseado nas equações anteriores, os valores iniciais para estas variáveis livres podem ser estimados através de cálculos manuais com modelos simplificados do transistor ou através da metodologia gm/I<sub>D</sub> utilizando a curva I<sub>D</sub> x I<sub>N</sub>.

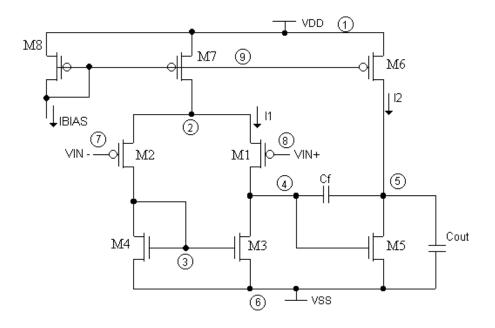

### 2.4.2 Amplificador OTA Miller

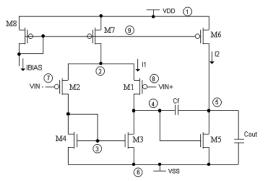

O amplificador operacional de transcondutância tipo Miller, ou simplesmente OTA Miller, é um amplificador composto por dois estágios, sendo o primeiro estágio formado por um amplificador diferencial e o segundo formado por um amplificador inversor. Na interligação entre os estágios é utilizado um capacitor (Cf) para melhorar a estabilidade do circuito (ALLEN, 2002). O esquemático do amplificador OTA Miller é mostrado na FIGURA 10.

O estágio amplificador diferencial é o mesmo mostrado na seção anterior, porém neste circuito ele é constituído por um par diferencial (M1 e M2) com transistores do tipo P. Com isso, o espelho de corrente de carga ativa (M3 e M4) é formado por transistores do tipo N e o espelho de corrente de polarização (M7 e M8) é formado por transistores do tipo P. O estágio amplificador inversor é formado pelos transistores M5 e M6. Assumindo que o transistor M1 possua o mesmo tamanho do transistor M2, o transistor M3 o mesmo tamanho de M4 e M7 igual a M8, como variáveis livres de projeto tem-se W e L dos transistores M1, M3, M5, M6 e M7 e a fonte de corrente de polarização Ibias, totalizando 11 variáveis livres de projeto.

Com a utilização da metodologia  $gm/I_D$  o circuito tem como variáveis livres o L e o valor de  $gm/I_D$  de cada um dos transistores, onde a partir da curva  $gm/I_D$  x  $I_N$ , pode-se calcular a largura W do canal dos transistores e a fonte de corrente de polarização (IBIAS).

FIGURA 10 - Esquemático do Amplificador OTA Miller

As principais especificações deste circuito são as mesmas apresentadas no amplificador diferencial. Porém, como o amplificador tipo Miller possui um estágio de saída torna-se interessante a análise dos níveis máximos e mínimos da tensão de saída. Estes níveis de tensão são relacionados pela especificação *output swing*.

O ganho em baixa freqüência (Av<sub>0</sub>) pode ser calculado com a seguinte equação:

$$Av_0 = \left(\frac{gm}{I_D}\right) \cdot \left(\frac{1}{VA_1} + \frac{1}{VA_3}\right)^{-1} \cdot \left(\frac{gm}{I_D}\right) \cdot \left(\frac{1}{VA_5} + \frac{1}{VA_6}\right)^{-1}$$

(14)

onde VA é a tensão de Early dos transistores M1, M3, M5 e M6.

O produto ganho-largura de faixa (GBW) é calculado com a equação abaixo:

$$GBW = \frac{g_{m1}}{C_f} \tag{15}$$

onde gm1 é a transcondutância do transistor 1 e  $C_f$  é a capacitância de acoplamento entre os estágios do amplificador.

O Slew Rate é calculado com a equação (16), onde  $I_3$  é a corrente de dreno do transistor M3.

$$SR = \frac{I_3}{C_f} \tag{16}$$

Os valores mínimos e máximos de ICMR podem ser calculados com as equações (17) e (18) onde  $V_{DD}$  e  $V_{SS}$  são os valores de tensão de alimentação do circuito,  $V_{DSSAT}$  representa o valor de tensão entre os terminais de dreno e source necessário para que o transistor opere em saturação e  $V_G$  é a tensão de gate.

$$ICMR^{+} = V_{DD} + V_{DSSAT7} + V_{G1}$$

(17)

$$ICMR^{-} = V_{SS} + V_{G3} + V_{DSSAT1} - V_{G1}$$

(18)

Os valores de *output swing* são calculados pelas seguintes equações:

$$OS + = V_{DD} - V_{DSSAT6} \tag{19}$$

$$OS - = V_{SS} + V_{DSSAT5} \tag{20}$$

Baseado nas equações anteriores, os valores inicias para estas variáveis livres podem ser estimados de maneira tradicional, ou seja, através de cálculos manuais e de modelos simplificados do transistor, ou ainda através da metodologia gm/I<sub>D</sub>.

#### 2.5 Medição de especificações de amplificadores através da simulação elétrica

As especificações do circuito podem ser avaliadas de acordo com as equações simplificadas apresentadas na seção anterior. Porém devido às simplificações e à simplicidade das expressões, muitos fatores são desprezados. Neste intuito, uma maneira eficiente de medir o valor das especificações é através da simulação elétrica, uma vez que os simuladores utilizam modelos que possuem uma série de parâmetros de tecnologia de forma a aproximar o comportamento real do dispositivo.

Assim são utilizadas configurações de circuitos de forma a medir as principais especificações do circuito através das três análises de um simulador SPICE: análise AC (domínio da frequência), análise DC (variação no nível de tensão ou corrente) e análise transiente (domínio do tempo).

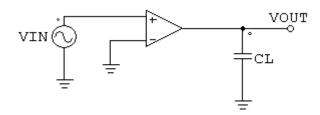

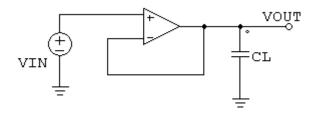

Para medir o ganho em baixas frequências (Av<sub>0</sub>), o produto ganho-largura de faixa (GBW) e margem de fase (PM) é efetuado a análise AC do circuito. Uma configuração para medir o ganho em malha aberta do circuito é mostrada na FIGURA 11.

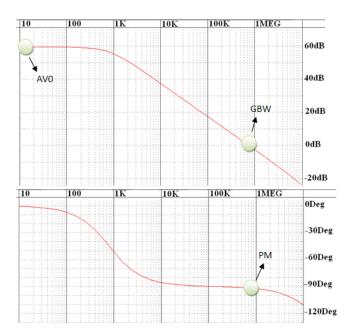

Da resposta desta simulação extrai-se o diagrama de bode, que relaciona o módulo do ganho e a fase do circuito no domínio da freqüência, como mostrado na FIGURA 12, onde são extraídas as três especificações de interesse.

FIGURA 11 – Circuito de simulação para a medição de Avo, GBW e PM.

FIGURA 12 – Diagrama de Bode da análise AC do circuito da FIGURA 11.

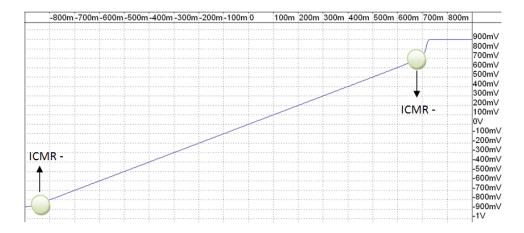

Para obter o valor de ICMR, mínimo e máximo, através de simulação é utilizado um amplificador operacional em configuração de ganho unitário. Nesta simulação varia-se a tensão de entrada de um valor mínimo a um valor máximo, através de uma análise DC do simulador, e verificam-se graficamente os limites de tensão de entrada em que a relação entrada-saída é mantida unitária.

FIGURA 13 – Configuração para medição de ICMR com análise DC.

A FIGURA 14 mostra a curva de relação entre a tensão de entrada e de saída, resultante da simulação, onde são verificados os limites da região onde é mantida a relação unitária entre a tensão de saída e de entrada. Nestas regiões define-se como ICMR mínimo e máximo o valor de tensão de entrada destes pontos.

FIGURA 14 – Relação de entrada e saída para a medição do ICMR resultante da simulação do circuito da FIGURA 13.

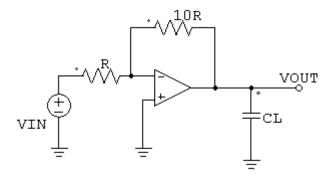

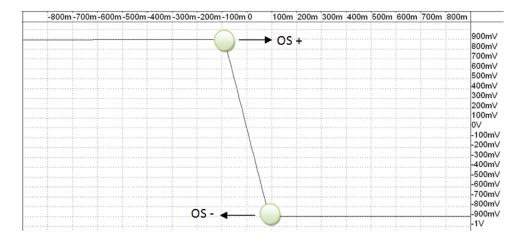

Para medir o nível mínimo e máximo da tensão de saída (output swing) o amplificador operacional é configurado como um amplificador inversor. O ganho da configuração deve ser escolhido de forma que a variação no sinal de entrada faça com que a saída do circuito, caso o amplificador seja ideal, opere alem dos valores nominais. Isto faz com que o amplificador real sature nos valores mínimos e máximos da tensão de saída.

A FIGURA 15 mostra o circuito com um ganho de tensão igual -10, para medição do output swing. Neste circuito, fazendo-se uma análise DC do simulador, de forma a variar a tensão de entrada de um valor mínimo a um máximo, o gráfico da FIGURA 16 é obtido. Neste gráfico, são tomados os valores de tensão de saída limites em que a linearidade de ganho igual a -10 é mantida sem saturação.

FIGURA 15 – Configuração para medição do Output Swing.

FIGURA 16 – Relação de entrada e saída para a medição do output swing resultante da simulação do circuito da FIGURA 15.

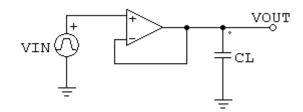

Para a medição da velocidade de resposta do amplificador (Slew Rate) é utilizado o circuito mostrado na FIGURA 17. Esta simulação se refere à análise da resposta ao degrau do circuito através da verificação da tensão de saída devido à ocorrência de um pulso na entrada do amplificador. Para esta medição é efetuada uma análise transiente no circuito.

Uma típica curva de resposta a simulação é mostrada na FIGURA 18, sendo que o slew rate se refere à taxa de subida desta curva (medida em V/µs).

FIGURA 17 – Circuito para medição de SR.

FIGURA 18 – Resposta de simulação do circuito da FIGURA 17 para medição do slew rate.

#### 2.6 Conclusão

Neste capítulo foram apresentados os dispositivos MOSFETs e as suas principais características físicas e elétricas, as metodologias de dimensionamento de transistores baseadas nas equações simplificadas do circuito e na curva gm/ID e a análise de duas topologias de amplificadores operacionais. Foram também analisadas formas de medição das principais especificações de circuitos amplificadores operacionais através de simulação elétrica SPICE.

Com este capítulo, pode-se verificar que o projeto de um circuito integrado analógico é uma tarefa complexa, uma vez que é necessário explorar um espaço de projeto de várias variáveis restrito pelas especificações de projeto.

Foram apresentadas neste capítulo as duas topologias de amplificadores operacionais que serão utilizadas no decorrer deste trabalho para a análise das metodologias que serão detalhadas. Porém a metodologia que será proposta não se restringe somente a estes circuitos, sendo possível a utilização em outros blocos analógicos.

# 3 FERRAMENTAS DE AUXÍLIO AO PROJETO DE CIRCUITOS INTEGRADOS ANALÓGICOS E HERÍSTICAS DE OTIMIZAÇÃO

## 3.1 Introdução

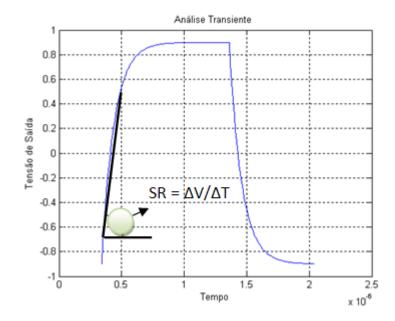

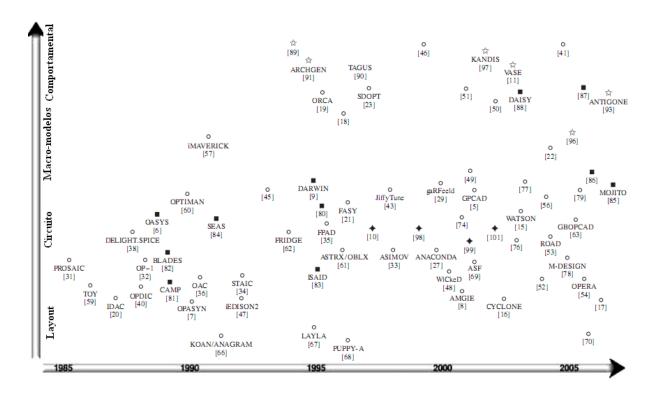

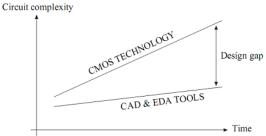

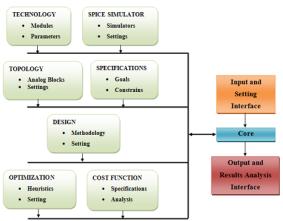

O projeto de circuitos integrados vem cada vez mais necessitando de ferramentas de auxílio ao projeto, tanto de ferramentas de simulação quanto de ferramentas de automação de projeto. Segundo (HÄGGLUND, 2003), as ferramentas computacionais de auxílio ao projeto possuem um crescimento que não acompanha a evolução da tecnologia CMOS, fazendo com que exista uma lacuna entre complexidade da tecnologia e a complexidade para quais as ferramentas estão disponíveis, conforme mostra o gráfico da FIGURA 19.

No campo de circuitos integrados digitais, ambas as ferramentas de simulação e de síntese automática estão bem desenvolvidas. Assim, é possível projetar um circuito integrado utilizando o fluxo de projeto dado por uma série de ferramentas, desde a sua descrição, em linguagens de descrição de hardware, até o leiaute do circuito com células lógicas (RABAEY, 2003)

Nos circuitos integrados analógicos as ferramentas de auxílio ao projeto ainda são pouco desenvolvidas e em sua maioria são ferramentas para simulação, análise de variabilidade do circuito (análise de piores casos e Monte Carlo, por exemplo) e ferramentas de desenho de lei-aute customizado. Apesar do tema não ser novo (DEGRAUWE,1987) e de existirem inúmeros trabalhos de pesquisa (GIRARDI, 2003, GIELEN,G.G, 2000), até hoje não existem ferramentas ou metodologias de projeto que automatize totalmente o projeto analógico.

O principal objetivo destes trabalhos é a melhor exploração do espaço de projeto de forma a reduzir o tempo de busca e também fazer otimizações em grandezas do circuito como potência dissipada e área ocupada, características estas que são fundamentais para circuitos que consomem pouca energia e tenham tamanho reduzido.

O grande problema no desenvolvimento deste tipo de ferramenta é a grande complexidade envolvida, pois a modelagem dos circuitos analógicos é altamente não-linear. Com isso as ferramentas tendem a automatizar somente partes do projeto.

FIGURA 19 – Evolução da complexidade da tecnologia CMOS e das ferramentas de auxílio ao projeto (HÄGGLUND, 2003).

#### 3.2 Ferramentas de Projeto Analógico

Até o que se sabe não existe nenhuma ferramenta computacional que automatize todas as etapas de projetos de um circuito integrado analógico, desde a escolha de topologias em nível de sistemas até o desenho do leiaute do circuito integrado. O que se tem atualmente são ferramentas que automatizam somente parte do projeto ou que servem de auxílio aos projetistas para tomada de decisões.

Em nível de circuito, as ferramentas dividem-se basicamente em dois grupos quanto ao tipo de análise: baseada em equações ou baseadas em simulação SPICE. No primeiro grupo os

circuitos são dimensionados de acordo com as equações simplificadas ou com modelos compactos do circuito. Neste tipo de ferramenta normalmente o tempo de busca de soluções é pequeno, devido ao projeto tratar-se de um processamento de equações. Porém, quando há algumas simplificações nestas equações, a qualidade da solução muitas vezes se distancia dos

valores reais.

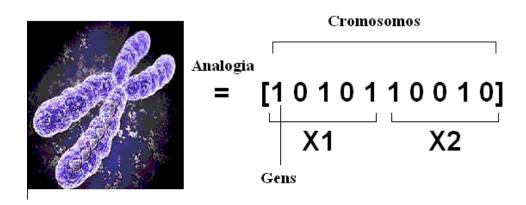

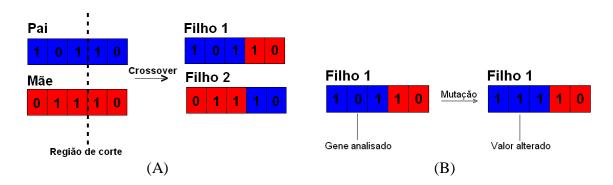

Nas ferramentas baseadas em simulações são utilizados simuladores tipo SPICE para avaliar as especificações do circuito. Como os simuladores utilizam modelos matemáticos que contêm inúmeros parâmetros para a aproximação com os dispositivos reais, são obtidos resultados próximos da realidade. O grande problema desta forma de análise é que, dependendo do tipo de exploração, são realizadas milhares de simulações na busca de uma solução otimizada, fazendo com que o tempo de execução destas ferramentas seja longo.