# FEDERAL UNIVERSITY OF PAMPA

# **ADRIANO MARQUES GARCIA**

TOWARDS A BENCHMARK FOR PERFORMANCE AND POWER CONSUMPTION EVALUATION OF PARALLEL PROGRAMMING INTERFACES

# **ADRIANO MARQUES GARCIA**

# TOWARDS A BENCHMARK FOR PERFORMANCE AND POWER CONSUMPTION EVALUATION OF PARALLEL PROGRAMMING INTERFACES

Master's Thesis submitted to the Graduate Program in Electrical Engineering of Federal University of Pampa in partial fulfillment of the requirements for the degree of Master in Electrical Engineering.

Supervisor: Prof. Dr. Alessandro Gonçalves Girardi

Co-supervisor: Prof. Dr. Claudio Schepke

Alegrete 2019

# Ficha catalográfica elaborada automaticamente com os dados fornecidos pelo(a) autor(a) através do Módulo de Biblioteca do Sistema GURI (Gestão Unificada de Recursos Institucionais).

G216t Garcia, Adriano Marques

Towards a benchmark for performance and power consumption evaluation of parallel programming interfaces / Adriano Marques Garcia.

78 p.

Dissertação(Mestrado) -- Universidade Federal do Pampa, MESTRADO EM ENGENHARIA ELÉTRICA, 2019.

"Orientação: Alessandro Gonçalves Girardi".

1. Análise de desempenho. 2. Consumo de Energia. 3. Programação Paralela. I. Título.

# Adriano Marques Garcia

# TOWARDS A BENCHMARK FOR PERFORMANCE AND POWER CONSUMPTION EVALUATION OF PARALLEL PROGRAMMING INTERFACES

Master's Thesis submitted to the Graduate Program in Electrical Engineering of Federal University of Pampa in partial fulfillment of the requirements for the degree of Master in Electrical Engineering.

Master's Thesis defended and passed in 25th march 2019 Examination board

Prof. Dr. Alessandro Gonçalves Girardi

Supervisor UNIPAMPA

Prof. Dr. Claudio Schepke

Co-supervisor

UNIPAMPA

Prof. Dr. Arthur Francisco Lorenzon

UNIPAMPA

Prof. Dr. Dalvan Jair Griebler

PUCRS

Prof. Dr. João Vicente Ferreira Lima

UFSM

#### **RESUMO**

Este trabalho apresenta um conjunto de pseudo-aplicações e propõe que sejam utilizadas como um benchmark para avaliar desempenho e consumo de energia de diferentes Interfaces de Programação Paralela (IPPs). O conjunto consiste de 11 pseudo-aplicações implementadas usando as IPPs: PThreads, OpenMP, MPI-1 e MPI-2. Essas IPPs foram escolhidas por serem compatíveis com a maioria das arquiteturas multinúcleo atuais. Estudos anteriores usaram essas pseudo-aplicações para realizar esse tipo de avaliação em diferentes arquiteturas, pois não há outro benchmark que ofereça essa variedade de pseudo-aplicações implementadas em todas essas IPPs, usando diferentes modelos de comunicação (memória compartilhada ou troca de menssagens). Trabalhos relacionados mais recentes que comparam IPPs precisam procurar diferentes alternativas para resolver o problema, pois não há um benchmark que supra essa demanda. O objetivo deste trabalho é propor o uso dessas pseudoaplicações como um benchmark para avaliar desempenho e consumo de energia de diferentes IPPs. Para alcançar esse objetivo, são analisados o comportamento das pseudo-aplicações e IPPs em relação aos acessos à memória cache, desvios e operações de ponto-flutuante. Os resultados dos experimentos mostraram que existe uma boa distribuição entre pseudo-aplicações que fazem um uso mais ou menos intensivo desses parâmetros. Além disso, é feito um estudo de caso para avaliar o desempenho, o consumo de energia e o consumo de potência (potência dissipada) dessas pseudo-aplicações. Os resultados mostram que as pseudo-aplicações em geral possuem um bom desempenho. Apesar do consumo de energia ser, em alguns casos, 300 vezes maior entre diferentes pseudo-aplicações com MPI por conta das diferentes características e parâmetros de cada aplicação, essa diferença não aparece na potência dissipada. As aplicações e as IPPs mostraram fazer um uso dos recursos de hardware de uma forma bem dinâmica e nossos resultados mostram que elas são capazes de ser representativas em diferentes cenários. Portanto esse conjunto pode sim ser utilizado como um benchmark paralelo.

Palavras-chave: benchmark, desempenho, consumo de energia.

#### **ABSTRACT**

This work presents a set of pseudo-applications and proposes them to be used as a benchmark to evaluate the performance and power consumption of different Parallel Programming Interfaces (PPIs). The set consists of 11 algorithms implemented in PThreads, OpenMP, MPI-1, and MPI-2 (spawn) PPIs. These PPIs were chosen because they are compatible with most of the current multi-core architectures. Previous studies have used some of these pseudo-applications to perform this type of evaluation in different architectures since there is no benchmark that offers this variety of PPIs and communication models. Recent related work that compare PPIs have looked for different alternatives to solve the problem since the available parallel benchmarks do not meet this demand. The goal of this work is to propose the use of these pseudo-applications as a benchmark to evaluate the performance and power consumption of different PPIs. To achieve this goal, we analyze the behavior of pseudo-applications and PPIs with respect to cache access, branches, and floating point operations. The results of these experiments showed that there is a good balance among pseudo-applications that make more or less intensive use of these parameters. In addition, we conducted a case study to evaluate the performance, energy consumption, and power consumption (power dissipation) of these pseudo-applications. The results show that the pseudo-applications generally have a good performance. Although the total energy consumption is, in some cases, 300 times greater among different MPI pseudo-applications, this difference does not appear in the power consumption. The PPIs and the pseudo-applications presented to use the hardware resources in a very dynamic way and our results show that they are able to represent different scenarios. Therefore they can be used as a parallel benchmark.

**Keywords**: benchmark, performance, energy consumption.

# **LIST OF FIGURES**

| Figure 1 – Low L3 cache accesses per kilo instructions rate                 | 48 |

|-----------------------------------------------------------------------------|----|

| Figure 2 – Medium L3 cache accesses per kilo instructions rate              | 49 |

| Figure 3 - High L3 cache accesses per kilo instructions rate                | 50 |

| Figure 4 – Low branch instructions per kilo total instructions rate         | 52 |

| Figure 5 - Medium branch instructions per kilo total instructions rate      | 52 |

| Figure 6 - High branch instructions per kilo total instructions rate        | 53 |

| Figure 7 — Floating-point operations per kilo instructions                  | 55 |

| Figure 8 – Low floating-point operations per kilo instructions rate         | 56 |

| Figure 9 — High floating-point operations per kilo instructions rate        | 57 |

| Figure 10 – Energy consumption and performance for each pseudo-application. | 59 |

| Figure 11 – Power consumption for CPU-bound pseudo-applications             | 62 |

| Figure 12 – Power consumption for memory-bound pseudo-applications          | 63 |

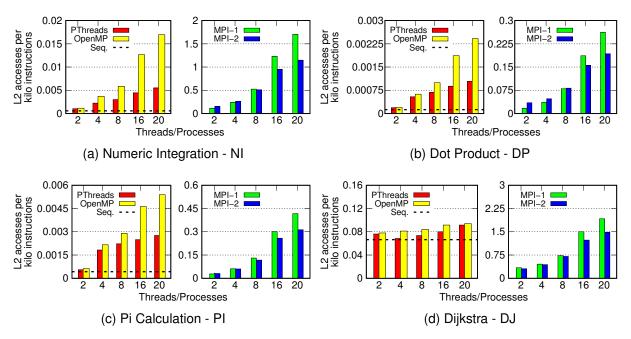

| Figure 13 – L2 cache accesses per kilo instructions (A)                     | 77 |

| Figure 14 – L2 cache accesses per kilo instructions (B)                     | 78 |

# **CONTENTS**

| 1      | INTRODUCTION                          | 15 |

|--------|---------------------------------------|----|

| 1.1    | Objectives                            | 17 |

| 1.2    | Structure of the Work                 | 18 |

| 2      | BACKGROUND                            | 19 |

| 2.1    | Benchmarks                            | 19 |

| 2.2    | Parallel Programming Interfaces       | 20 |

| 2.3    | Hardware Performance Counters         | 21 |

| 2.4    | Related Work                          | 21 |

| 2.4.1  | Similar Benchmarks                    | 22 |

| 2.4.2  | Comparison Among Benchmarks           | 24 |

| 3      | BENCHMARK PSEUDO-APPLICATIONS         | 27 |

| 3.1    | Pseudo-applications Description       | 27 |

| 3.1.1  | Numeric Integration                   | 27 |

| 3.1.2  | PI Calculation                        | 28 |

| 3.1.3  | Dot Product                           | 29 |

| 3.1.4  | Harmonic Sums                         | 29 |

| 3.1.5  | Odd-Even Sort                         | 30 |

| 3.1.6  | Discrete Fourier Transform            | 30 |

| 3.1.7  | Turing Ring                           | 31 |

| 3.1.8  | Dijkstra                              | 33 |

| 3.1.9  | Jacobi Method                         | 33 |

| 3.1.10 | Matrix Multiplication                 | 34 |

| 3.1.11 | Gram-Schmidt                          | 35 |

| 3.2    | Parallelizing the Pseudo-Applications | 36 |

| 3.3    | Historic of Classifications           | 37 |

| 3.4    | Source Code Improvements              | 39 |

| 4      | EXPERIMENTAL RESULTS                  | 45 |

| 4.1    | Methodology                           | 45 |

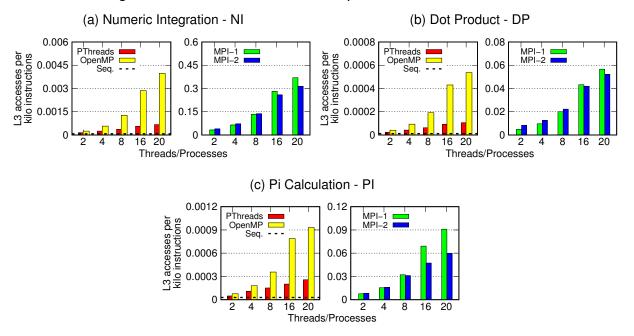

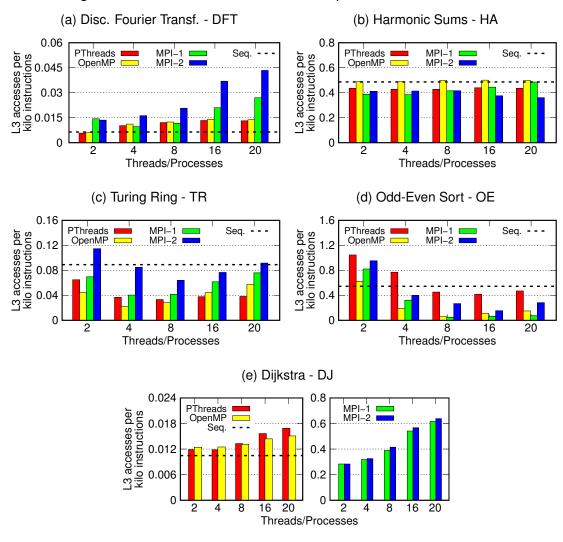

| 4.2    | Cache Memory Accesses                 | 47 |

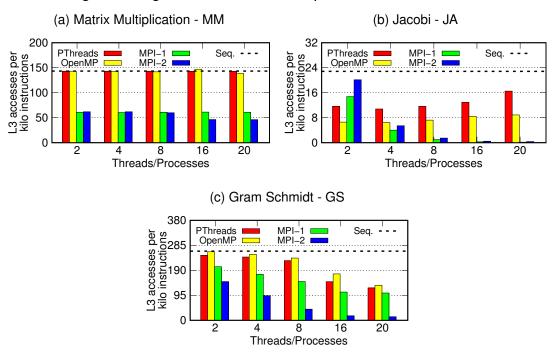

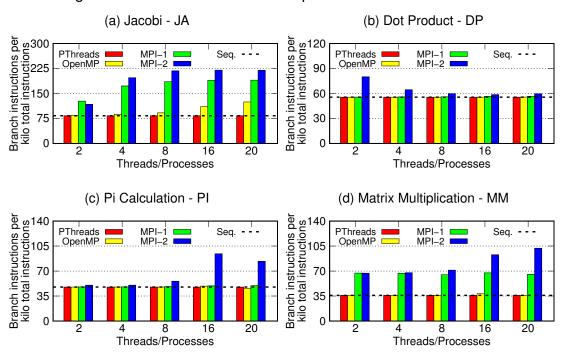

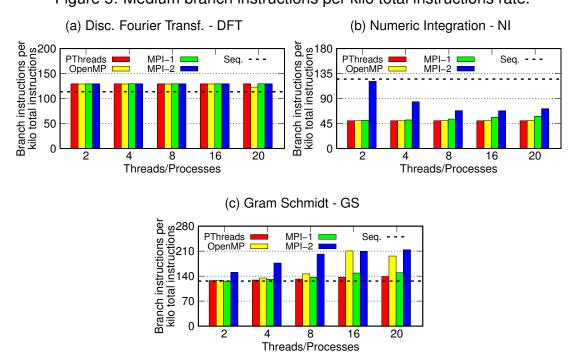

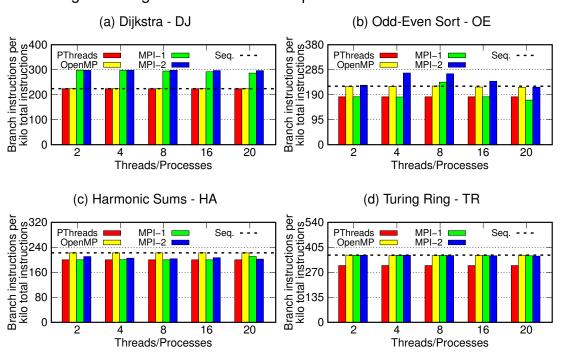

| 4.3    | Branch Instructions                   | 51 |

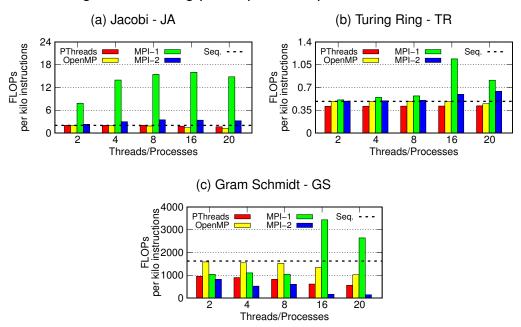

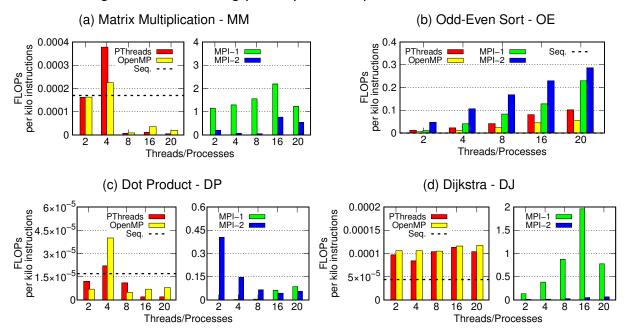

| 4.4    | Floating-Point Operations             | 54 |

| 4.5    | Performance and Energy Consumption    | 57 |

| 4.6    | Power Consumption                     | 60 |

| 4.7    | Results Discussion                    | 64 |

| 5      | CONCLUSION                            | 67 |

| BIBLIOGRAPHY                           | 69 |  |

|----------------------------------------|----|--|

| APPENDIX                               | 75 |  |

| APPENDIX A – L2 CACHE ACCESSES RESULTS | 77 |  |

#### 1 INTRODUCTION

Multi-core processors have now become mainstream for both general-purpose and embedded computing (SEZNEC, 2016). In addition, manycore processors are being extensively used in embedded and high-performance computing systems. This transition created a disruptive change: substantial performance gains for applications can no longer be achieved without modifying the underlying source code. The increase in processing power of small processors, the popularization of artificial intelligence, and the growth of IoT will mean that small devices can (and need to) process larger volumes of information. This is called edge computing, where applications do local processing, without having to send all information to be processed in a data center, for example. The trend is that all devices present on this edge will have a multi-core architecture capable of doing parallel processing (ROMAN; LOPEZ; MAMBO, 2018). Sensing devices, for example, often can not wait for the response time of a server (which tends to increase along with the increase of these devices) and will need to make faster decisions. This way, although there are many kinds of applications that cannot be executed in parallel because their nature, many of the future applications should be radically different, they must be parallel.

In the past, the major goal of parallelizing an application was to achieve maximum performance. However, today there is also a growing concern about the energy consumption of these parallel applications. There are two main fronts that motivate this concern. The first one is that many countries are limiting the use of existing supercomputers because of their high energy consumption, such as United States, Japan, and China (Bourzac, Katherine, 2017). The other one is that embedded processors tend to outperform server and general-purpose processors in the multi-core processor market in the following years. Currently, general-purpose processors represent a 53% share of the market, while embedded processors and mobile SoC MPUs account for 47% (IC-INSIGHTS, 2018). This way, in addition to the power limitations imposed on supercomputers, we will soon have this concern for the vast majority of processors.

The embedded processor industry have reshaped by some factors, among them, the slowing of Moore's Law and the realization that most devices will emphasize price and power rather than speed. Most embedded applications do not need leading-edge performance, but they do want the best power efficiency (the ratio of the output power divided by the input power) and the lowest power consumption (BOLARIA; HALFHILL, 2017). Therefore, it is necessary to find efficient ways to identify the best trade-offs between performance and power consumption of these applications.

The performance increase is reached with faster multiple parallel processors. Parallel computing aims to use multiple processors to execute different parts of the same program simultaneously (RAUBER; RÜNGER, 2010). However, processors

should be able to exchange information at a certain point in the execution time. While tasks parallelism makes it possible to increase the performance, the use of more processors and the need for communication among them can lead to an increase in energy consumption.

The parallelism can be explored with different Parallel Programming Interfaces (PPIs), each one having specific characteristics in terms of synchronization and communication. In addition, the performance gain may vary according to processor architecture and hierarchical memory organization, communication model of each PPI, and also with the complexity, problem type, and other characteristics of the application.

So far, software developers have been hesitant to burden themselves with the difficult and error-prone task of parallelizing their programs. This difficulty already begins when it is necessary to choose which PPI or programming language should be used to parallelize a particular application. As parallelism is becoming more popular and a necessity for many applications, more ways to use it will be developed. An example of this is the Threading Building Blocks (TBB) which is a C++ template library recently developed by Intel<sup>®</sup> for parallel programming on multi-core processors (INTEL, 2018). Another example is the InKS (EJJAAOUANI et al., 2018), which is a new programming model to decouple performance from algorithms in HPC codes.

Each PPI has its own characteristics that can behave in different ways in each architecture, according to the application that will run in that system. Finding out which type of parallelization provides the best trade-off between performance and power consumption is still a manual task based on previous experiences or studies. The question here is: how much performance gain outweighs the extra energy expenditure? A benchmark which provides different types of pseudo-applications implemented in several Parallel Programming Interfaces could be useful to answer this question. However, we did not found a benchmark offering a good set of pseudo-applications, fully parallelized, using multiple PPIs and different models of communication between tasks. The most commonly used parallel benchmarks have only partial parallel sets using more than one PPI (e.g. NPB, PARSEC, SPEC) and many researchers need to find other alternatives to fill this lack, as we expose in our related work.

To fill this gap, this work proposes a new benchmark using a set of 11 pseudo-applications developed with the purpose of evaluating the performance and energy consumption in multi-core architectures. These pseudo-applications were parallelized using parallel tasks and classified according to different criteria in previous studies (LORENZON et al., 2015; LORENZON; CERA; BECK, 2015; LORENZON, 2014; GARCIA, 2016). These studies have shown that these pseudo-applications have characteristics distinct enough to represent different scenarios, such as different amount of communication among tasks, and high and low usage of CPU and memory. This work is a continuation of those previous studies that have been cited, from Lorenzon

1.1. Objectives 17

(2014) to Garcia (2016).

# 1.1 Objectives

In this work we use a set of 11 parallel pseudo-applications that were used to measure performance and power consumption in multi-core architectures in previous studies. These applications were implemented for specifics contexts and architectures and were not ready to be available as a benchmark for the general users. They presented very poor usability and most of them did not work properly with different or new architectures or compilers. These 11 pseudo-applications are implemented in PThreads, OpenMP, MPI-1, and MPI-2 (spawn) PPIs and these PPIs were chosen because they are compatible with most multi-core architectures.

The main objective of this work is to do the first move to turn this set of parallel algorithms into a real benchmark. A benchmark to evaluate the performance and power consumption of different parallel programming interfaces. To achieve this goal we re-coded the pseudo-applications, fixed the errors, and added some new features, such as dynamic parameters, small running interface (bash scripts), results generation, configuration files, and put the set available in a public repository online. We also conduct case studies where we evaluate different parts of the system that can improve or worsen the impact of the pseudo-applications. First we evaluated the cache accesses, to see how memory accesses impact on the performance and power consumption. We also measure the branches to evaluate the branch predictor, and the floating-point operations to evaluate the floating-point unit performance.

In addition, we measured the performance and energy consumption and used them to obtain power consumption (energy consumed over time). It will allow us to observe the scalability of pseudo-applications in the architecture used and the impact of their characteristics on power consumption. To improve the understanding of the results, in the end, we summarize these results in a table which shows an overview of them. The contributions of this work are as follows:

- The set of pseudo-applications did not have a complete formal description. In our work we describe the equations, data structures and algorithms implemented by each pseudo-application;

- The source code of the pseudo-applications had many static parameters, and many errors and bugs. In this way, the pseudo-applications presented very poor usability. So we rewrote many parts of the source code and fixed the problems, increasing portability and usability;

- We extend the work from Lorenzon (2014) on performance, power consumption, and memory access of pseudo-applications by doing a case study of them in

a more robust architecture and also analyzing Floating-Point Operations and Branches.

#### 1.2 Structure of the Work

The remainder of this work is organized as follows. In the chapter 2 we present the PPIs in which the pseudo-applications are implemented, the way we will evaluate the pseudo-applications, and the related work, where we compare our work with similar benchmarks. The chapter 3 presents the set of pseudo-applications and the techniques used to parallelize them, bringing more details about the historic of classifications. At the end of this Section we also show all the improvements and modifications we had apply on the source-codes.

In chapter 4, section 4.1 shows how our experiments were structured and brings some information to a better understanding of the results. section 4.2 presents the results of cache memory accesses, section 4.3 presents the branches results, and FLOPs results are presented in section 4.4. The section 4.5 and section 4.6 brings results of performance and energy, and power consumption respectively. In the section 4.7 we discuss and summarize the results. Finally, in chapter 5 we draw our final conclusions and future works.

#### 2 BACKGROUND

In computing, there has always been a need to compare, classify, or test the performance of different systems for a variety of purposes. With the evolution of these systems, it became impracticable to do this task through simple tests and comparison of the specifications of each architecture (GRAY, 1992). At this point, it was necessary to create a way to standardize a method that would meet this growing need. To supply this need were created benchmarks, which are now used in various areas of computing.

One of the areas that needs to be constantly testing efficiency and comparing system performance is the High Performance Computing area. In this area we aim to increase the performance of a given application, usually through the use of parallel programming. According to Rauber e Rünger (2010), the parallelization consists of dividing the tasks of an application and executing them concurrently in order to reduce its total execution time. Its use becomes essential in scientific applications that require high computational power, such as calculations of weather forecasting, calculations of DNA and genome sequences, among other different applications. More recently, with the popularization of multi-core architectures, general-purpose applications (image and sound filters, graphic editors, internet servers, etc.) have also taken advantage of parallel programming.

Parallelising an application may not be an easy task. For this, PPIs are able to make this process less arduous for the programmer. However, each interface has its own characteristics and specifications that must be carefully studied to implement a parallel application. The programmer must follow some basic care, paying attention to which parts of the code will be executed simultaneously and, depending on the interface, must also define how the data will be communicated and synchronized.

This chapter gives a brief description of each parallel programming interface in section 2.2. Section 2.3 briefly discusses how hardware counters are used by similar works. In section 2.4 related work and benchmarks are presented, where a comparison of these benchmarks is made with the benchmark proposed in this work.

#### 2.1 Benchmarks

The evolution of computational architectures has made comparing the performance of different computing systems, only looking at their specifications a difficult task. Historically, manufacturers used to classify the performance of their systems using a variety of different metrics. This generated a lot of confusion among consumers and often this information might not be credible. To solve this problem, a group of manufacturers came together to develop standardized test sets for measurements on these systems, allowing these results to be compared between different (SPEC, 2018) architectures. This process was also intended to educate consumers about the performance of their

products. It was in this context that benchmarks emerged.

In computing, benchmarking is the action of comparing the relative performance of an object or product by running a computer program (GRAY, 1992). To extract correct data on different products and objects, in order to compare them uniformly, a series of standard tests and tests are performed. The term benchmark is commonly used to define the programs developed to run this testing process. Along with this, the term benchmarking is associated with the process of evaluating the characteristics and performance of a computer hardware, such as the performance of the FPU of FPU.

In this work, we will study a benchmark to measure the performance and energy consumption of different PPI in multi-core architectures. These PPIs work in any multi-core architecture. The benchmark currently consists of 11 parallel applications implemented using four different PPIs, PThreads, OpenMP, MPI-1 and MPI-2.

# 2.2 Parallel Programming Interfaces

There are several computational models used in parallel computing, such as data parallelism, shared memory, message passing, and operations in remote memory. These models differ in several aspects, such as whether the available memory is locally shared or geographically distributed, and volume of communication (GROPP; LUSK; THAKUR, 1999). In this work, the set of pseudo-applications were implemented using two communication models with the four PPIs: PThreads, OpenMP, MPI-1, and MPI-2.

The OpenMP pattern consists of a series of compiler directives, function libraries, and a set of environment variables that influence the execution of parallel programs (RAUBER; RÜNGER, 2010). These directives are inserted into the sequential code and the parallel code is generated by the compiler from them. This interface operates on the basis of the thread fork-join execution model.

Different from OpenMP, in POSIX Threads (PThreads) the parallelism is explicit through library functions. That is, the programmer is responsible for managing *threads*, workload distribution, and execution control (BUTENHOF, 1997). PThreads comprises some subroutines that can be classified into four main groups: thread management, mutexes, condition and synchronization variables.

Applications deployed with MPI-2 can begin the execution with a single process. Then, the primitive  $\texttt{MPI\_Comm\_spawn}$  () can be used for the creation of processes

dynamically. A process of an MPI application, which will be called by the parent, invokes this primitive. This invocation causes a new process, called a child, to be created, which not need to be identical to the parent. After creating a child process, it will belong to an intra-communicator and the communication between parent and child will occur through this intra-communicator. In the child process, the execution of the function MPI\_Comm\_get\_parent() is responsible for returning the intercom that links it to the parent. In the parent process, the inter-communicator that binds the child is returned in the execution of the function MPI\_Comm\_spawn().

#### 2.3 Hardware Performance Counters

To evaluate the pseudo-applications, this work uses Hardware Performance Counters (HPCs) which are available on most current processors. Essentially, hardware performance counters are a tool that is used by software engineers to measure performance and for allowing software vendors to enhance their code such that performance improves (UHSADEL; GEORGES; VERBAUWHEDE, 2008). Hardware performance counters are exposed to the user space on commercial hardware. The performance counters monitor CPU, memory, network and I/O by counting specific events such as cache misses, pipeline stalls, floating point operations, bytes in/out, bytes read/write, and also information about energy consumption (WU; TAYLOR, 2016).

Compared to software profilers, hardware counters provide low-overhead access to a wealth of detailed performance information about the CPU's functional units, caches, main memory etc (UHSADEL; GEORGES; VERBAUWHEDE, 2008). Another benefit of using them is that no source code modifications are needed in general. However, the types and meanings of hardware counters vary from one kind of architecture to another due to the variation in hardware organizations.

Regarding to energy consumption, there are many other previous work on power modeling and estimation that are based on HPCs (LIVELY et al., 2014) (LIVELY et al., 2012) (SONG et al., 2013) (RODRIGUES et al., 2013) (CHETSA et al., 2014). These approaches used HPCs to monitor the system components such as CPU, memory, disk, I/O, and GPU. The methods then correlated these performance counters with the power consumed by each system component to derive a power model for each system component.

#### 2.4 Related Work

Many studies that want to perform comparisons between PPIs need to modify and re-code applications from a parallel benchmark or to use more than one benchmark. It is demonstrated by some previous works. There is a work (ISIDRO-RAMIREZ; VIVEROS; RUBIO, 2015) in which the authors implemented some HPL benchmark

applications in PThreads and Java Threads in order to evaluate the power consumption of these PPIs in an ARM Cortex-A9 processor. Also, in another study Popov et al. (2015) needed to re-implement a set of NAS applications in OpenMP to test the Parallel Codelet Extractor and REplayer (PCERE). In order to make an evaluation between OpenMP and MPI optimized to work with shared memory on a single node (MPI-3), Jain et al. (2018) had to use different benchmarks for the experiments. In another work, Dosanjh et al. (2019) had to modify the MPI Sandia Microbenchmarks (SMBs) (DOEFLER; BARRETT, 2009) to use multithreading. These are some examples that it would be interesting to have a single standard benchmark in order to generate useful data for comparing PPIs in different computational systems.

All the work mentioned above had a major problem to solve and it was necessary to implement or modify existing benchmarks to solve it. However, there is a second group of related work in which building a new benchmark class is part of the major goal. These second group aims to reimplement a whole set of applications, or part of it, into another PPI or programming language. To fill the lack of portability to C++ language of the NAS legacy codes, Griebler et al.(GRIEBLER et al., 2018) described the NAS Kernel applications in C++. They also implemented these new codes using Intel TBB, OpenMP, and FastFlow interfaces in order to compare the performance achieved by different parallel implementations. The PARSEC benchmark originally has parallel implementations with high-level abstraction, it uses pragma-based PPIs such as OpenMP and Intel TBB. Thus, Danelutto et al.(DANELUTTO et al., 2017) identified the lack of low-level mechanisms and implemented P³ARSEC, a subset of this benchmark using POSIX Threads.

The third group of related work is the already consolidated parallel benchmarks. Through a bibliographic study, we searched for benchmarks that have similar purposes and the same target architectures of the benchmark proposed in this work. Therefore, we have considered benchmarks that provide a set of parallel applications for embedded or general-purpose multi-core architectures. In this way, we identify and present in Subsection 2.4.1 the following benchmarks: ALPBench, PARSEC, ParMiBench, SPEC, Linpack, NAS, and Adept Project.

#### 2.4.1 Similar Benchmarks

ALPBench (University of Illinois, 2018) consists of a set of parallelized complex media applications gathered from various sources and modified to expose thread-level and data-level parallelism. It consists of 5 applications parallelized with PThreads. This benchmark is focused on general-purpose processors and has an open source license.

PARSEC (Princeton Application Repository for Shared-Memory Computers) is an open source benchmark suite (Princeton University, 2018). It consists of 11 applications, some parallelized using OpenMP, or PThreads or Intel TBB. The suite

2.4. Related Work 23

focuses on emerging workloads and was designed to contain a diverse selection of applications that are representative of next-generation shared-memory programs for chip-multiprocessors.

ParMiBench is an open source benchmark that specifically serves to measure performance on embedded systems that have more than one processor (IQBAL; LIANG; GRAHN, 2010). This benchmark organizes its applications into four categories and domains: industrial control and automotive systems, networks, office devices, and security. Its set consists of 7 parallel applications implemented using PThreads.

SPEC (SPEC, 2018) is a closed source benchmark but offers academic licenses. This benchmark is intended for general purpose architectures, but is subdivided into several groups with specific target architectures, and can be used for several purposes, such as Java servers, file systems, high-performance systems, CPU tests, among others. We consider the following groups of SPEC: SPEC MPI2007, SPEC OMP2012, and SPEC Power. They were chosen because they are the ones who have at least one kind of parallel applications on their sets. SPEC MPI2007 is a set of 18 applications deployed in MPI focused on testing high-performance computers. SPEC OMP2012 uses 14 scientific applications implemented in OpenMP, offering optional energy consumption metrics based on SPEC Power. Finally, SPEC Power tests the energy consumption and performance of servers using CPU/Memory-Bound applications implemented in C and Fortran.

HPL consists of a software package that solves arithmetic dual floating-point precision random linear systems in high-performance architectures (PETITET, ). It runs a testing and timing program to quantify the accuracy of the solution obtained, as well as the time it took to compute. HPL code is open and consist of 7 applications form a collection of subroutines in Fortran, mostly CPU-Bound. Parallel implementations use MPI. HPL is the benchmark that makes up the so-called *High-Performance Computing Benchmark Challenge*, which is a list of the 500 fastest high-performance computers in the world.

The NAS Parallel Benchmarks (BAILEY et al., 1991) is a small set of open source programs that serve to evaluate the performance of parallel supercomputers. The benchmark is derived from physical applications of fluid dynamics and consists of four cores and three pseudo-applications. It is an open source benchmark and the pseudo-applications are implemented with MPI and OpenMP. Some applications are also implemented in HPF, UPC, Java, Titanium, TBB etc.

The Adept Benchmark (Adept-Project, 2018) is used to measure the performance and energy consumption of parallel architectures. Its code is open and is divided into 4 sets: Nano, Micro, Kernel and Application. The Micro suite, for example, consists of 12 sequential and parallel applications with OpenMP, focusing on specific aspects of the system, such as process management, caching, among others. On the other hand,

| Rating criteria                                  | ALPBench | PARSEC | ParMiBench | SPEC  | HPL | NAS | Adept | Our<br>benchmark |

|--------------------------------------------------|----------|--------|------------|-------|-----|-----|-------|------------------|

| Number of applications                           | 5        | 11     | 7          | 14-18 | 7   | 7   | 10-12 | 11               |

| Number of PPIs                                   | 1        | 3      | 1          | 2     | 1   | 2   | 3     | 4                |

| Number of communication models                   | 1        | 1      | 2          | 1     | 1   | 2   | 2     | 2                |

| Set of applications implemented in multiple PPIs |          |        |            |       |     | X   |       | X                |

| Open source                                      | X        | X      | X          |       | X   | X   | Х     | X                |

Table 1: Comparison of our benchmark with the similar ones

Source: by the author.

the Kernel set has 10 applications implemented sequentially and parallel with OpenMP, MPI and one of them in UPC (Unified Parallel C).

# 2.4.2 Comparison Among Benchmarks

The benchmark addressed in this work consist of 11 pseudo-applications implemented in C and their complexities range from O(n) to  $O(n^3)$ . All pseudo-applications are parallelized in 4 PPIs: PThreads, OpenMP, MPI-1 and MPI-2. These PPIs are the target of this work because they are the most widespread in the academic field and also because they are supported by most multi-core architectures, both embedded and general purpose. Therefore, the purpose of this benchmark is to provide the user with a tool to evaluate the performance and energy consumption of different PPIs in multi-core architectures.

We analyze the main characteristics of the related parallel benchmarks and compare to the benchmark we propose in this work in Table 1. In regarding to the benchmarks, some use only one PPI while others use more than one. However, some of those who use more than one PPI do not have the whole set of applications paralleled by all PPIs. They implement parts of the set with one PPI and other parts with another PPI. NAS, for example, uses several other PPIs. However, virtually no pseudo-application is implemented in all PPIs. Many of them are not supported by any multi-core architecture (e.g. ARM Architecture, as showed by Lorenzon (2014)). Three of the benchmarks use PThreads, five of them use OpenMP, and four use MPI. ALPBench also uses Intel TBB and Adept uses UPC.

Thus, even if some of these benchmarks implement three different PPIs, none

2.4. Related Work

of them allow an efficient comparison between these PPIs and between different communication models. Also, they do not exploit the parallelism with dynamic process creation that MPI-2 offers. In this way, we do not find any other benchmark that uses different PPIs, different communication models and a completely parallelized set of applications. The exception is the NAS, but it only offers two PPIs. Therefore, none of them meets the objective of comparing parallel programming interfaces, which is the main objective of the benchmark we are proposing in this work.

#### **3 BENCHMARK PSEUDO-APPLICATIONS**

This chapter presents the pseudo-applications<sup>1</sup> that compose the benchmark in detail, as well as the methods and techniques of parallelization adopted. In section 3.1 are presented the sequential algorithms and their main characteristics. The strategies used in the parallelization of each of the pseudo-applications are detailed in section section 3.2. Finally, section 3.3 shows how these pseudo-applications have been used and classified since their implementations.

# 3.1 Pseudo-applications Description

These pseudo-applications were developed with the purpose of establishing a relationship between performance and energy consumption in multi-core architectures. The pseudo-applications described here were based in the ones originally developed by Lorenzon (2014). The main features of each are presented in this section. Each subsection below presents the pseudo-applications in their sequential versions and shows details about their complexities, their algorithms, and formulas.

#### 3.1.1 Numeric Integration

The integral of a function was originally created to determine the area under a curve in the Cartesian plane by means of approximation techniques. The process of calculating the integral of a function is called integration (STEWART, 2001). This pseudo-application integrates the function f(x) (3.3) in the [a,b] interval. The basic method involved in this approximation is called numerical quadrature and is expressed by the equation 3.1, where  $\alpha_i$  is real coefficient (weight of the function) and  $x_i$ , is a sampling point of [a,b] defined by equation 3.2. The algorithm 1, which has a complexity of O(n), represents this pseudo-application. It is ideal for evaluating the FPU because of its low complexity and high number of floating point operations.

$$\int_{b}^{a} f(x)dx \simeq \sum_{i=0}^{n} \alpha_{i} f(x_{i})$$

(3.1)

$$x_i = \frac{(n-i-1) \cdot (a + (i \cdot b))}{(n-1)}$$

(3.2)

Source codes available at https://github.com/adrianomg/PAMPAR

$$f(x) = \frac{50}{\pi \cdot (2500 \cdot (x^2 + 1))} \tag{3.3}$$

#### **Algorithm 1:** Numeric Integration

```

1 begin

2 | Set the number of iterations

3 | Set the limits a \in b

4 | for (From zero to number of iterations) do

5 | Calculate f(x) from a to b

6 | end

7 end

```

#### 3.1.2 PI Calculation

Pi  $(\pi)$  is an irrational value that establishes a numerical relationship between the perimeter of a circumference and its diameter (ROY, 1990). Pi is commonly represented with 52 decimal places when it is necessary to perform high precision calculations. However, this accuracy can be increased by computational algorithms. There are several methods for calculating the value of Pi, these involve approximations, successive approximations, and infinite series of sums, multiplications, and divisions. In this pseudo-application, we used the Gregory-Leibniz method that is established by the equation 3.4 (ANDREWS; ROY, 1999).

$$\sum_{n=0}^{\infty} \frac{(-1)^n}{2n+1} = \frac{\pi}{4} \tag{3.4}$$

Although the Gregory-Leibniz method is considered inefficient for a few iterations, the precision increases as the iterations of n are increased. It generates Pi with an accuracy of 5 decimal places after 500 thousand iterations and 10 decimal places with  $5\times 10^9$  iterations (BORWEIN; BORWEIN; DILCHER, 1989). The implementation of this algorithm is quite simple. It starts by defining the number of iterations to be calculated and in the sequence a loop applies the equation 3.4. The output consists of an approximate value for Pi. This algorithm is defined by the pseudo-code 2. It has complexity of O(n) and can represent applications with low complexity with average number of floating-point operations.

#### Algorithm 2: Pi Calculation

```

1 begin

```

- 2 Set the number of iterations

- for (From zero to number of iterations) do

- 4 Apply Gregory-Leibniz method

- 5 end

- 6 end

#### 3.1.3 Dot Product

The dot product is an operation between two vectors whose result is a real number (also called scalar). The dot product is used in Euclidean geometry and is a special case of inner product (BANCHOFF; WERMER, 2012). This pseudo-application calculates the dot product between a sequence of ordered values and another one of reverse ordering. This algorithm can be seen in the pseudo-code and is defined by the equation 3.5. Ilt can represent applications with simple integer calculations and low complexity (O(n)).

$$a \cdot b = \sum_{i=1}^{n} a_i b_i = a_1 b_1 + a_2 b_2 + \dots + a_n b_n$$

(3.5)

#### **Algorithm 3:** Dot Product

- 1 begin

- 2 Set the number of iterations

- for (From zero to number of iterations) do

- 4 Calculate the dot product

- 5 end

- 6 end

#### 3.1.4 Harmonic Sums

The Harmonic Sums or Harmonic Series is a finite series that calculates the sum of arbitrary precision after the decimal point (GOLDSTON; YILDIRIM, 2001). This mathematical sequence has this name because it has similar proportions to the wavelengths of a vibrating string. This sequence diverges slowly, as can be seen from the equation 3.6. This algorithm represents pseudo-applications with average number of branches and high number of FLOPs.

$$\sum_{i=1}^{n} \frac{1}{i} = 1 + \frac{1}{2} + \frac{1}{3} + \frac{1}{4} + \dots + \frac{1}{n}$$

(3.6)

This pseudo-application contains a vector that stores the precision sum for each i of the algorithm. Its main processing consists of successive operations of division and module calculation for each value of i. The output consists of the sum of these operations. This algorithm is described in the pseudo-code 4 and has complexity of  $O(n \times d)$ , where n is the number of iterations and d is the size of the vector.

```

Algorithm 4: Harmonic Sums

1 begin

Set the number of iterations

2

for (From zero to number of iterations) do

3

for (Iterate through the vector) do

4

Calculate the Harmonic Sum

5

Store the precision sum

6

end

7

end

8

for (Iterate through the vector) do

9

Decimal precision adjustment

10

end

11

12 end

```

#### 3.1.5 Odd-Even Sort

Odd-Even sort is a sorting algorithm that compares all the indexed (odd-even) pairs of adjacent elements in the list. If a pair is in the wrong order (the first is greater than the second), it swaps the elements. The next step repeats this for the indexed (even-odd) pairs of adjacent elements. It then toggles between (odd-even) and (even-odd) steps until the list is sorted (KNUTH, 1998). The output of this algorithm is the ordered input vector. Its implementation is represented by the algorithm 5 and is based on bubble-sort. Its complexity is  $O(n^2)$  and this pseudo-application is suitable for evaluating the PPI performance under the presence of a high number of branches.

#### 3.1.6 Discrete Fourier Transform

The discrete Fourier transform (DFT) converts a finite sequence of equally-spaced samples of a function into an equivalent-length sequence of equally-spaced samples of the discrete-time Fourier transform (DTFT), which is a complex-valued function of frequency (SMITH; STEVEN et al., 1997). This way, the resulting frequency values are integer multiples of a fundamental frequency whose period corresponds to the length of the sampling interval. This function is widely used in digital signal processing and is defined by the equation 3.7, where: N is the number of samples; n

# Algorithm 5: Odd-Even Sort

```

1 begin

Set number of elements (n)

2

for (Iterate through the vector) do

3

for (from 0 to n-1 step 2) do

if (Element at current position is higher than element at next position)

5

then

Swap elements

6

end

7

end

8

for (From 1 to n-1 step 2) do

9

if (Element at current position is higher than element at next position)

10

then

11

Swap elements

end

end

13

end

14

15 end

```

is the current sample (from 0 to N-1);  $x_n$  is the signal level at time n; k is the current frequency (from 0 Hz to N-1 Hz); and  $X_k$  is the level of the frequency k on the signal.

$$x_n = \frac{1}{N} \sum_{k=0}^{N-1} X_k \cdot \left( \cos \left( 2\pi k \frac{n}{N} \right) + j \sin \left( 2\pi k \frac{n}{N} \right) \right), \quad n \in \mathbb{Z}$$

(3.7)

The algorithm has two main loops to calculate the sum of the real and imaginary terms that compose the equation. These calculations are performed separately and summed at the end, as can be seen in the pseudo-code 6. The algorithm has  $O(n^2)$  complexity and is suitable for representing CPU-bound applications with high number of FLOPs.

#### 3.1.7 Turing Ring

Alan Turing analyzed the interaction of two chemicals in a ring of cells using two differential equations coupled to describe a prey/predator system (TURING, 1952). It is a space system in which predators and prey interact in the same environment. The system simulates the iteration and evolution between prey and predator through the use of two differential equations 3.8 and 3.9.  $r_{x,y}$  are the birth rates,  $c_{a,b}$  represent local interactions,  $\mu_{x,y}$  are migration rates between neighbouring cells and the predator and prey populations in location i are represented by  $X_i, Y_i$ . Evolution is defined according

# Algorithm 6: Discrete Fourier Transform

```

1 begin

for (Iterate through the vector) do

2

for (Iterate through the vector) do

3

Calculate the real part of the function

4

end

5

for (Iterate through the vector) do

6

Calculate the imaginary part of the function

7

end

8

Sum the two parts and store the result in the solution vector

end

10

11 end

```

to the neighbouring cells (PAUDEL; AMARAL, 2011).

$$\frac{dX_i}{dt} = X_i(r_x + c_{xx}X_i + c_{xy}Y_i) + \mu_x(X_{i+1} + X_{i-1} - 2X_i)$$

(3.8)

$$\frac{dY_i}{dt} = Y_i(r_y + c_{yx}X_i + c_{yy}Y_i) + \mu_y(Y_{i+1} + Y_{i-1} - 2Y_i)$$

(3.9)

The algorithm consists of an input matrix containing in each position the number of predators and prey, which will interact for n evolutions producing an output (matrix) society. This algorithm is represented by the pseudo-code 7 and has complexity of  $O(m \times n^2)$ , where m is the number of evolutions of the society and n the size of the matrix. This application has a high number of branches.

#### **Algorithm 7:** Turing Ring

```

1 begin

Set the number of evolutions

2

for (From zero to the number of evolutions) do

3

for (Iterate through the matrix rows) do

4

for (Iterate through the the matrix Columns) do

5

Simulate the evolution by applying the differential equations Store

6

the solution in an auxiliary matrix

end

7

end

8

for (Iterate through the matrix rows) do

for (Iterate through the matrix columns) do

10

Store the auxiliary array data in the original array

11

end

12

end

13

end

14

15 end

```

# 3.1.8 Dijkstra

The Dijkstra algorithm, designed by the Dutch computer scientist Edsger Dijkstra, solves the shortest path problem in a directed or non-directed graph with non-negative weight edges. Given a source vertex in the graph, the algorithm finds the least cost path between this vertex and any other vertex (DIJKSTRA, 1959).

Our implementation uses an adjacency matrix of size  $N \times N$ . Considering n being the number of vertices, the complexity of the algorithm is  $O(n^2)$ . However, our pseudo-application considers the smallest path from n to n vertices, bringing its total complexity to  $O(n^3)$ . The output of this pseudo-application is a vector containing the minimum distance between each of the vertices as output. It is represented in the pseudo-code 8. This pseudo-application do only integer operations and has an average number of branches.

```

Algorithm 8: Dijkstra

1 begin

for (Travel vertices) do

2

for (Iterate through the distances vector) do

3

Set the maximum possible distance to all vertices

Set each vertex as unvisited

5

end

6

Set NULL distance to the source vertex

7

for (Iterate through the vertices) do

8

for (Iterate through the vertices) do

if (If the vertex is a neighbor and has not yet been visited) then

10

Update current vertex in the array

11

end

12

end

13

Set current vertex as visited for (Iterate through the distances vector)

14

do

if (Check if it is the shortest path) then

15

Update the path in the distances vector

16

end

17

end

18

end

19

end

20

21 end

```

#### 3.1.9 Jacobi Method

Jacobi method is a classical method dating back to the late eighteenth century. Iterative techniques are rarely used to solve linear systems of small dimensions, since the time required to obtain a minimum precision exceeds that required by direct techniques like the Gaussian Elimination (BURDEN; FAIRES; REYNOLDS, 2001). However, for

large systems, with a high percentage of null inputs (sparse systems), these techniques appear as more efficient alternatives. Considering a linear system Ax = b, where A is the matrix of the coefficients  $m \times n$ , x is the vector of variables,  $x^k$  is the  $k^{\text{th}}$  iteration of x, and b the vector of the constant terms. The objective of the method is to find an approximate result for x through the convergence of vectors (PRESS et al., 2007). The equation 3.10 represents this method.

The Jacobi method is an algorithm for determining the solutions of a diagonally dominant system of linear equations (BURDEN; FAIRES; REYNOLDS, 2001). It is a classical method dating back to the late eighteenth century. Iterative techniques are rarely used to solve linear systems of small dimensions, since the time required to obtain a minimum precision exceeds that required by direct techniques like the Gaussian Elimination (BURDEN; FAIRES; REYNOLDS, 2001). However, for large systems, with a high percentage of null inputs (sparse systems), these techniques appear as more efficient alternatives. Considering a square linear system Ax = b, where A is the  $n \times n$  coefficients matrix, x is the vector of variables and b is the vector of the constant terms, the objective of the method is to find an approximate result for x through the convergence of vectors(PRESS et al., 2007) by using equation 3.10.  $x^k$  is the kth iteration of x.

$$x_i^{(k+1)} = \frac{1}{a_{ii}} \left( b_i - \sum_{j \neq i} a_{ij} x_j^{(k)} \right), i = 1, 2, \dots, n.$$

(3.10)

The program consists of a repetition loop in which each iteration scrolls the target matrix and applies the Jacobi method. The algorithm performs operations on a single matrix and this generates dependence on data. To work around this problem, an auxiliary matrix is used, which will contain the correct value at the end of each computation. This algorithm is described in the pseudo-code 9. It is a  $O(n^3)$  memory-bound pseudo-application and has few branches and FLOPs.

#### 3.1.10 Matrix Multiplication

There are several methods for performing matrix multiplication. The pseudo-application that we use in our work implements the most common method (PRESS et al., 2007). It consists of the multiplication of matrix A rows elements by the matrix B columns elements, storing the result in a matrix C. This is an  $O(n^3)$  algorithm and it represents applications with high number of memory accesses. It is represented by the pseudo-code 10.

$$C = (AB)_{ij} = \sum_{k=1}^{n} a_{ik} b_{kj} = a_{i1} b_{1j} + a_{i2} b_{2j} + \dots + a_{in} b_{nj}.$$

(3.11)

## Algorithm 9: Jacobi Method

```

1 begin

Set the number of iterations

2

for (From zero to number of iterations) do

3

for (Iterate through the matrix rows) do

for (Iterate through the matrix columns) do

5

Apply Jacobi Method

6

Store the result in an auxiliary matrix

7

end

8

end

9

Copy the data from the auxiliary matrix to the solution matrix

10

11

12 end

```

# Algorithm 10: Matrix Multiplication

```

1 begin

for (Iterate through the rows) do

2

for (Iterate through the columns) do

3

for (Iterate through the elements) do

4

Multiply rows elements and columns elements

5

Store the result in the solution matrix

6

end

7

end

8

end

9

10 end

```

### 3.1.11 Gram-Schmidt

The Gram-Schmidt algorithm is a method for orthonormalising a set of vectors in an inner product space (CHENEY; KINCAID, 2009). It is a  $O(n^3)$  algorithm and is representative for applications with high number of memory accesses, branches, and FLOPs. This algorithm receives a finite and linearly independent set of vectors  $S = u_1, \ldots, u_n$  and returns an orthonormal set  $S' = v_1, \ldots, v_n$  which generates the same initial subspace S. It performs a series of projection operations between the input

vectors. Each vector  $v_i$  is calculated as:

$$v_{1} = u_{1}$$

$$v_{2} = u_{2} - \frac{\langle u_{2}, v_{1} \rangle}{\langle v_{1}, v_{1} \rangle} v_{1}$$

$$v_{2} = u_{3} - \frac{\langle u_{3}, v_{1} \rangle}{\langle v_{1}, v_{1} \rangle} v_{1} - \frac{\langle u_{3}, v_{2} \rangle}{\langle v_{2}, v_{2} \rangle} v_{2}$$

$$\vdots = \vdots$$

$$v_{n} = u_{n} - \frac{\langle u_{n}, v_{1} \rangle}{\langle v_{1}, v_{1} \rangle} v_{1} - \frac{\langle u_{n}, v_{2} \rangle}{\langle v_{2}, v_{2} \rangle} v_{2} - \dots - \frac{\langle u_{n}, v_{n-1} \rangle}{\langle v_{n-1}, v_{n-1} \rangle} v_{n-1}$$

$$(3.12)$$

The inner product between u and v can be calculated as:

$$\langle v, u \rangle = v_1 u_1 + \dots + v_n u_n \tag{3.13}$$

The algorithm has as its input an array of vectors. After successive computations in n steps a new output matrix is generated. These steps are computed one after another, where the computation of n+1 depends on the result of n. This algorithm is represented by the pseudo-code 11 and its complexity is  $O(n^3)$ .

```

1 begin

for (Iterate through the matrix rows) do

for (Iterate through the matrix columns) do

3

Calculate the inner product

4

5

end

for (Iterate through the matrix columns) do

6

Calculate the resulting vector norm

7

end

for (Iterate through the matrix columns) do

for (Iterate through the matrix elements) do

10

Normalize the vector and store in the solution matrix

11

```

# 3.2 Parallelizing the Pseudo-Applications

Algorithm 11: Gram-Schmidt

end

end

end

12

13

14

15 end

Parallelize a sequential program can be done in several ways. However, inappropriate techniques can negatively impact the performance of an algorithm. To minimize this problem, all parallel implementations in this work were based on statements from (FOSTER, 1995; BUTENHOF, 1997; GROPP; LUSK; THAKUR, 1999; RAUBER; RÜNGER, 2010). Rauber e Rünger (2010) propose that the parallelization must be done in a systematic way. According to them, there are three fundamental steps for the parallelization of a sequential algorithm, which are: computation decomposition; assigning tasks to processes/threads; and mapping processes/threads into physical processing units.

The decomposition of the computation and assignment of tasks to process-es/threads occurred explicitly in the parallelization with PThreads and MPI-1 and -2, in order to obtain the best workload balancing. Also, message exchange functions between processes were included, as well as the dynamic creation of processes in MPI-2. For parallelization with OpenMP, parallel loops with thin and coarse granularity were used. According to (FOSTER, 1995; RAUBER; RÜNGER, 2010), this technique is most appropriate for parallelizing algorithms that perform iterative calculations and traverse contiguous data structures (e.g. matrix, vector, etc.). For each data structure, a specific parallelization model was adopted.

#### 3.3 Historic of Classifications

The set of pseudo-applications that compose the benchmark have already been investigated in previous works. The pseudo-applications were used in these works to analyze performance and energy consumption on embedded systems and general purpose processors. In (LORENZON; CERA; BECK, 2015; LORENZON, 2014; LORENZON; CERA; BECK, 2014) the authors classified the pseudo-applications between CPU-Bound, Weakly Memory-Bound and Memory-Bound, according to the following criteria:

- Reads/writes to memory represents the number of accesses to the shared and private memory addresses of the processor, considering read and write operations for each pseudo-application;

- 2. **Data dependence** means that at least one thread/ process can only start its execution when the computation result of one or more threads/ processes is over. This shows the existence of communication between threads/processes;

- 3. **Synchronization points** determine that at certain times during the execution of an pseudo-application, all threads/processes will need to be synchronized before a new task starts.

- 4. **Thread-Level Parallelism** shows how busy the processor is during pseudo-application execution;

5. **Communication rate** - represents the volume of communication required by threads/processes during pseudo-application execution.

In (LORENZON et al., 2015), the authors used the number of data exchange operations as a criterion for classification. In the PPI target, these operations represent barriers, locks/unlocks and threads/processes creation or termination. Using this criterion, the pseudo-applications were divided between High and Low Communication. The main problem with both classifications is that they were not done uniformly with all pseudo-applications. The first classification used some pseudo-applications with a specific interface, while another configuration was used to do a second classification. Hence, the four PPIs were never evaluated together. TLP, for example, was collected only for 9 pseudo-applications and using only PThreads.

Already using the first criterion (access read/write to shared memory), the pseudo-applications were classified between CPU-Bound and Memory-Bound. However, this type of data does not indicate how much CPU was actually used by a particular pseudo-application. An pseudo-application that performs many accesses to shared memory could also have a high CPU usage. In the opposite case, an pseudo-application with few accesses to memory and previously classified as CPU-Bound could also make less use of CPU in regarding to the other pseudo-application classified as Memory-Bound.

After that, in (GARCIA; SCHEPKE, 2018; GARCIA, 2016) the authors investigated the impact of each PPI on the use of CPU and memory. In these studies, the authors classified the pseudo-applications in such a way that all scenarios analyzed contained at least one pseudo-application with: high CPU usage and high memory usage; high CPU usage and low memory usage; low CPU usage and high memory usage; or low CPU and memory usage. Finally, (LORENZON; CERA; BECK, 2016) used some of these pseudo-applications to verify the best performance and energy consumption in different multi-core architectures. All the previous research using these pseudo-applications went at this point. Here starts our contributions.

Gathering all these previous studies, it was concluded that this set contained pseudo-applications diverse enough to characterize a benchmark. After all, they were being used as a benchmark, but an effort was needed to unify them, to analyze the whole set together and prepare them for use by others. The first thing we had to do was fixing the source codes to ensure the correctness of the pseudo-applications outputs. Many of them presented errors when it has some of its parameters modified. Second problem we had to care about was the usability of these pseudo-applications. For the user it could be very confusing to understand how to use and set all the parameters needed for running them.

## 3.4 Source Code Improvements

The original benchmark suite, provided by Lorenzon (2014), needed some modifications in order to perform the experiments and make the suite closer to a benchmark. We made updates on these pseudo-applications to be used in a wide range of scenarios. The size of the input problem was somewhat static and not compatible with the declared data type. Many pseudo-applications stored values greater than the capacity of the designated data type and this led to erroneous outputs. The GCC compiler, which was used with the original pseudo-applications, is able to work around this problem in some cases, but other compilers may not. So we had to sort this out.

Another problem was that many parallel pseudo-applications had static workload balancing for at most 8 parallel tasks only. So we had to implement dynamic workload balancing that works for all pseudo-applications and for any number of parallel tasks. In addition, this workload balancing was defined for a single input problem size. In the Listing 3.1 there is an example of what the original defineChunk function was like.

```

1 void defineChunk(int nTasks) {

if(nTasks == 2) {

3

firstEven[0] = 0;

lastEven[0] = 74999;

4

5

firstEven[1] = 75000; lastEven[1] = N-1;

6

firstOdd[1] = 74999; lastOdd[1] = N-1;

7

}else if(nTasks == 3) {

firstEven[0] = 0; lastEven[0] = 49999;

8

9

10

firstEven[1] = 50000; lastEven[1] = 99999;

firstOdd[1] = 49999; lastOdd[1] = 99998;

11

firstEven[2] = 100000; lastEven[2] = N-1;

12

firstOdd[2] = 999999; lastOdd[2] = N-1;

13

}else if(nTasks == 4) {

14

15

else if(nTasks == 8)

16

17

18

}

19

20 }

```

Listing 3.1: Static function to set the size and amount of chunks.

In this Listing 3.1 the chunks are assigned statically to different numbers of tasks. This is a code piece extracted from the Odd-Even Sort application, and the global variable  ${\tt N}$  represents the size of the input vector (this works just for 150000 elements). The function shows that for each number of parallel tasks it needs to indicate the start and end of each chunk statically ono-to-one. That is, if the user wants to run the

application with an input vector of 150001 elements this will lead to inconsistent results. Also, if the user wants to run with 6 parallel tasks, it will not be possible either. So to improve the original implementation we implemented a new defineChunk function (Listing 3.2). With this new function it is possible to define any size of input problem and it will also work for any number of parallel tasks.

```

1 void defineChunk(int nTasks) {

int i;

3

int aux = N/nTasks;

4

for(i = 0; i < nTasks; i++){</pre>

5

firstEven[i] = i*aux;

6

lastEven[i] = ((i+1)*aux)-1;

7

if(i == 0){

8

firstOdd[i] = (i*aux)+1;

9

lastOdd[i] = ((i+1)*aux)-2;

}else if(i == nTasks-1) {

10

firstOdd[i] = (i*aux)-1;

11

lastOdd[i] = ((i+1)*aux)-1;

12

13

}else if (i != 0 \&\& i != nTasks-1) {

14

firstOdd[i] = (i*aux)-1;

lastOdd[i] = ((i+1)*aux)-2;

15

16

17

18 }

```

Listing 3.2: Dynamic function to set the size and amount of chunks.

These modifications needed to be made in many applications, including some with complex defineChunk functions that took a long time to construct the dynamic equations. The static function to distribute chunk to 2, 3, 4 and 8 tasks has 75 code lines (symbolized by the vertical ellipsis), while the new dynamic function was written in 18 code lines. So we can say that certainly implementing this kind of improvement is a big step towards improving usability and decreasing the complexity of understanding the application by the user.

Using the Odd-Even Sort application as an example, we address another type of problem that often appeared in the original MPI-1 applications. This application divides an interleaving vector between odd and even positions and sorts each part using Bubble Sort. In the original application for each number of parallel processes created there was a different bubbleSort function to execute the MPI\_Send and MPI\_Irecv commands statically. This can be seen in Listing 3.3.

```

void bubbleSort2Tasks() {

void bubbleSort4Tasks() {

int i, source;

}

```

```

6

for (i=0; i < (N/2) + 1; i++) {

7

sortEven(0);

MPI_Send(&vector[37499], 1, MPI_INT, 0, 99, interComm);

8

9

MPI_Irecv(&vector[37499], 1, MPI_INT, 0, 99, interComm, &request[0]);

sortOdd(0);

10

11

MPI_Wait(&request[0], MPI_STATUS_IGNORE);

12

MPI_Irecv(&vector[37499], 37500, MPI_INT, 0, 99, interComm, &request[0]);

13

MPI_Irecv(&vector[74999], 37500, MPI_INT, 1, 199, interComm,&request[1]);

14

MPI_Irecv(&vector[112499], 37501, MPI_INT, 2, 299, interComm,

15

&request[2]);

for (i=0; i<3; i++) {</pre>

16

MPI Waitany (3, request, &source, MPI STATUS IGNORE);

17

18

19 }

20 void bubbleSort8Tasks() {

21

22 }

23 :

```

Listing 3.3: Static function to define chunk parameters.

The approach used in the original bubleSort function was appalling. However it was easily solved. We need to take care of the case where there are only two parallel processes, because this case has a different flow. All other cases followed the same structure with each other and this was solved in few code lines in the bubleSort function improved, as seen in Listing 3.4.

```

1 void bubbleSort (int nTasks) {

2

int i, source = 0, aux = N/nTasks, id = 99;

3

for (i=0; i < (N/2) +1; i++) {</pre>

4

sortEven(0);

MPI_Send(&vector[aux-1], 1, MPI_INT, 0, id, interComm);

5

6

MPI_Irecv(&vector[aux-1], 1, MPI_INT, 0, id, interComm, &request[0]);

7

sortOdd(0);

8

MPI_Wait(&request[0], MPI_STATUS_IGNORE);

9

10

if(nTasks==2){

MPI_Recv(&vector[aux-1], (N-(aux-1))+1, MPI_INT, 0, id, interComm,

11

MPI_STATUS_IGNORE);

}else{

12

13

for (i=0; i<nTasks-1; i++)</pre>

MPI\_Irecv(\&vector[((i+1)*aux)-1], aux, MPI\_INT, i, id+(i*100),

14

interComm, &request[i]);

for (i=0; i < nTasks-1; i++)</pre>

15

```

Listing 3.4: Dynamic function to define chunk parameters.

Static functions to control interprocess communication was another problem often found in the original MPI applications. As can be seen in Listing 3.5, the startIrecv function runs the MPI\_Irecv command statically for 2, 3, 4, or 8 processes. Any other amount of parallel processes that the user sets will not work for this function. To solve this, we re-think this function so that the application works with any number of parallel processes. The current and improved version is in the Listing 3.6.

```

void startIrecv(int rank, int nTasks, ringStruct *game, int *vecEnd, int *

vecInit, int N) {

2

if(nTasks == 2){

3

if(rank == 0) {

4

MPI_Irecv(&game[(vecInit[1]*N)], N, MPI_INT, 1, 199, MPI_COMM_WORLD,

&req[0]);

}else{

5

6

MPI_Irecv(&game[(vecEnd[0]-1)*N], N, MPI_INT, 0, 99, MPI_COMM_WORLD,

&req[0]);

7

8

}else if(nTasks == 3){

9

if(rank == 0) {

10

MPI_Irecv(&game[(vecInit[1]*N)], N, MPI_INT, 1, 199, MPI_COMM_WORLD,

&req[0]);

} else if (rank == 1) {

11

MPI_Irecv(&game[(vecInit[2])*N], N, MPI_INT, 2, 299, MPI_COMM_WORLD,

12

&req[0]);

MPI_Irecv(&game[(vecEnd[0]-1)*N], N, MPI_INT, 0, 99, MPI_COMM_WORLD,

13

&req[1]);

14

else if(rank == 2){

MPI_Irecv(&game[(vecEnd[1]-1)*N], N, MPI_INT, 1, 399, MPI_COMM_WORLD,

15

&req[0]);

16

17

}else if(nTasks == 4) {

18

19

}else if(nTasks == 8){

20

21

22

23 }

```

Listing 3.5: Static function to start MPI Irecv.

```

void startIrecv(int rank, int nTasks, ringStruct *game, int *vecEnd, int *

vecInit, int N) {

```

```

if(rank == 0) {

3

MPI_Irecv(&game[(vecInit[rank+1]*N)], N, MPI_INT, rank+1, ((rank+1)*

100) +49, MPI_COMM_WORLD, &req[0]);

}else if(rank == (nTasks-1)) {

4

5

MPI_Irecv(&game[(vecEnd[rank-1]-1)*N], N, MPI_INT, rank-1, ((rank-1)*

100) +99, MPI_COMM_WORLD, &req[0]);

6

}else{

7

if(rank%2!=0){

MPI_Irecv(&game[(vecEnd[rank-1]-1)*N], N, MPI_INT, rank-1, ((rank-1)*

8

100) +99, MPI_COMM_WORLD, &req[0]);

9

MPI_Irecv(&game[(vecInit[rank+1]*N)], N, MPI_INT, rank+1, ((rank+1)*

100) +49, MPI_COMM_WORLD, &req[1]);

10

MPI_Irecv(&game[(vecInit[rank+1]*N)], N, MPI_INT, rank+1, ((rank+1)*

11

100) +49, MPI_COMM_WORLD, &req[0]);

MPI_Irecv(&game[(vecEnd[rank-1]-1)*N], N, MPI_INT, rank-1, ((rank-1)*

12

100) +99, MPI_COMM_WORLD, &req[1]);

13

14

}

15 }

```

Listing 3.6: Dynamic function to start MPI\_Irecv.

In addition to the code problems and dynamism, some modifications were necessary to improve more the usability of the pseudo-applications. The only way to change almost any execution parameter was by rewriting the source code, which was an inefficient way of doing this. So we've made all modifiable parameters dynamic and also added basic information on how to use them. In addition, we make the pseudo-applications available in an online repository<sup>2</sup> where we will add new updates and improve the source code documentation in the future.

<sup>&</sup>lt;sup>2</sup> Source codes available at https://github.com/adrianomg/PAMPAR

### **4 EXPERIMENTAL RESULTS**

In this chapter, we present our experimental results. The methodology we used for the experiments is described in Section 4.1. To identify which pseudo-applications make more accesses to the memory, in Section 4.2 we present cache memory accesses per instruction by pseudo-application. In Section 4.3 we organise the pseudo-applications according to the number of branch instructions. Section 4.4 presents the amount of floating-point operations each pseudo-application do per instruction. We carry out a case study in Section 4.5, where we evaluate the performance and energy consumption of the pseudo-applications. At the end, in Section 4.7, we discuss and summarise the results.

## 4.1 Methodology

The results presented in this chapter are the average of 30 executions. The executions are interleaved among the pseudo-applications. This number of executions was established as indicated in (HUNOLD; CARPEN-AMARIE, 2016). In this study, the authors perform experiments that show that the minimum number of executions is MPI in order to obtain statistically acceptable results. Following the indications of this study, the results in MPI-1 and MPI-2 showed an average absolute deviation bellow 3.7% in the worst cases. It means that the resulting data were very similar in each execution. OpenMP and PThreads showed an average absolute deviation below 1.3% in all cases. During the experiments, the computer remained locked to ensure that other pseudo-applications did not interfere actively with the results.

We use hardware counters to gather data about total instructions, cache accesses, branch instructions, and floating-point operations. Hardware counters are a set of special-purpose registers built into modern microprocessors to store the counts of hardware-related activities within computer systems. To access these hardware counters we use the PAPI (Performance Application Programming Interface) (TERPSTRA et al., 2010).

PAPI works by inserting directives within the application code. These directives use PAPI events, which are aliases for the native events identified by a hexadecimal value that points to a specific hardware counter. A big problem when using PAPI, or any other profiler, with parallel applications is to be able to pin all parallel tasks. This can be a challenge for a single parallel application, even using only one PPI. So to evaluate multiple applications and PPIs, and ensure reliable results, this can take a lot of time. In addition, writing directives in the pseudo-application codes is a not very efficient option to evaluate this amount of pseudo-applications.

To work around this problem, we decided to use an external C program that allows PAPI to be used without having to rewrite the pseudo-application code. This

| Data Structures   | Problem Size       | Acronym                                                                                                                                                                                                                      | Pseudo-Application                                                 | Complexity        |

|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------|

|                   | $10^{9}$           | NI                                                                                                                                                                                                                           | Numerical Integration                                              |                   |

| Unstructured data | $4 \times 10^{9}$  | PI                                                                                                                                                                                                                           | PI Calculation                                                     | O(n)              |

|                   | $15 \times 10^{9}$ | DP                                                                                                                                                                                                                           | Dot Product                                                        |                   |

|                   | $10^{5}$           | HA                                                                                                                                                                                                                           | Harmonic Sums                                                      | $O(n \times d)$   |

| Vector            | $25 \times 10^{4}$ | OE                                                                                                                                                                                                                           | Odd-Even Sort                                                      |                   |

|                   | 32768              | DFT                                                                                                                                                                                                                          | Discrete Fourier Transf.                                           | $O(n^2)$          |

|                   | 1920×1080          | HS                                                                                                                                                                                                                           | Histograms Similarity                                              |                   |

| Matrix            |                    | NI Numerical Integra  109 PI PI Calculation  109 DP Dot Product  HA Harmonic Sum  104 OE Odd-Even Sor  1080 HS Histograms Simila  GL Game of Life  TR Turing Ring  2048 DJ Dijkstra  JA Jacobi Method  MM Matrix Multiplicat |                                                                    | $O(m \times n^2)$ |

| IVIQUIA           | 2048×2048          | JA<br>MM                                                                                                                                                                                                                     | Dijkstra<br>Jacobi Method<br>Matrix Multiplication<br>Gram-Schmidt | $O(n^3)$          |

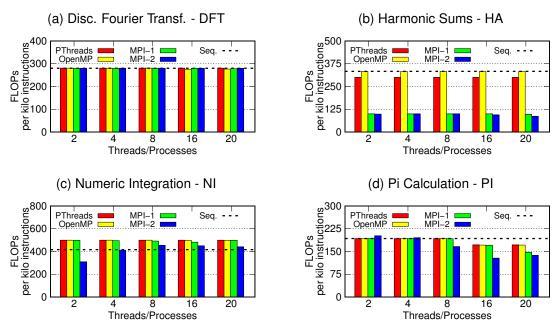

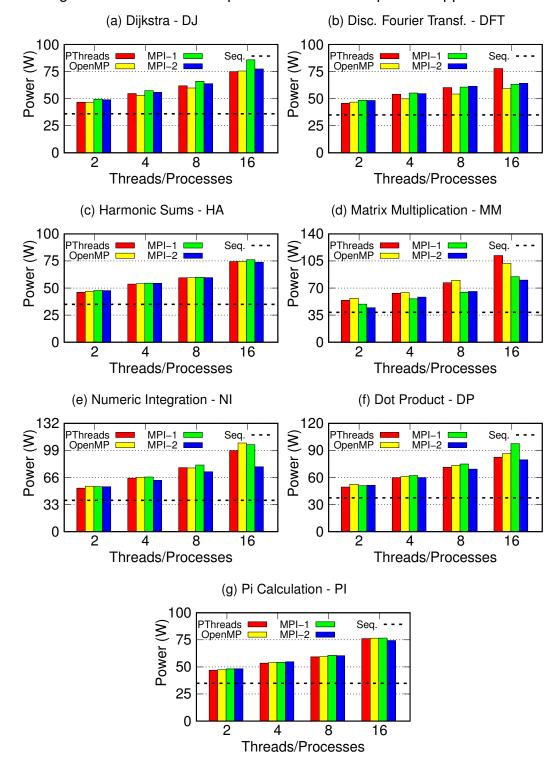

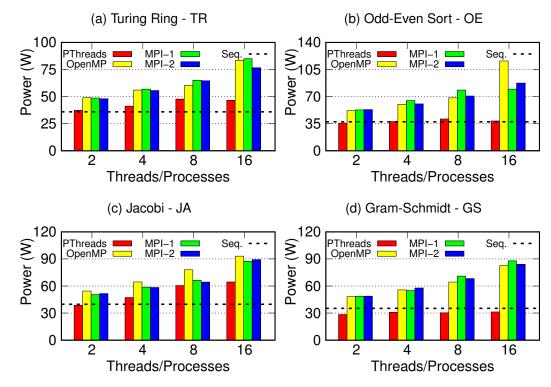

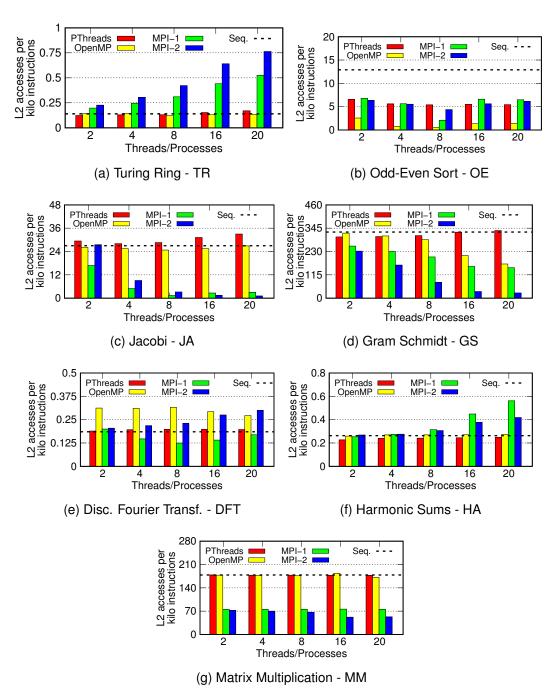

Table 2: Details about the applications